Madeo Synthesis

When addressing synthesis in Madeo, several levels are considered.

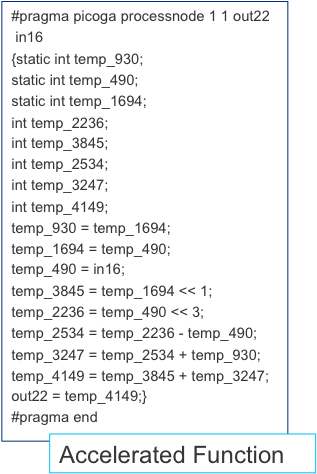

Primitives can be synthesized using :

- Madeo-FET, taking as input smalltalk untyped code + context

- Madeo-C, taking as input C code, can be translated to smalltalk so that to be accepted by Madeo- FET

Activities regarding system synthesis - mixing several target as in the Morpheus project - are described below:

System synthesizer

Biniou

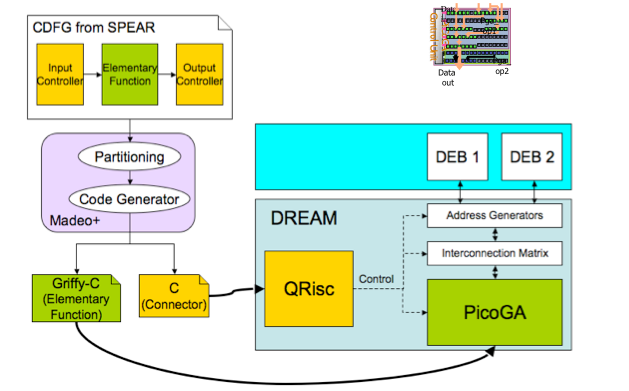

is a synthesizer addressing both the eFPGA from M2000/aboundLogic and

the midium grained DREAM platform from ARCES.

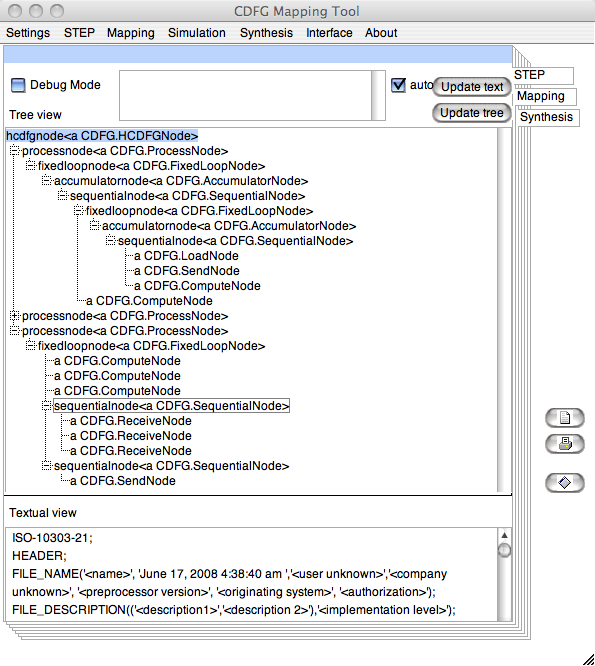

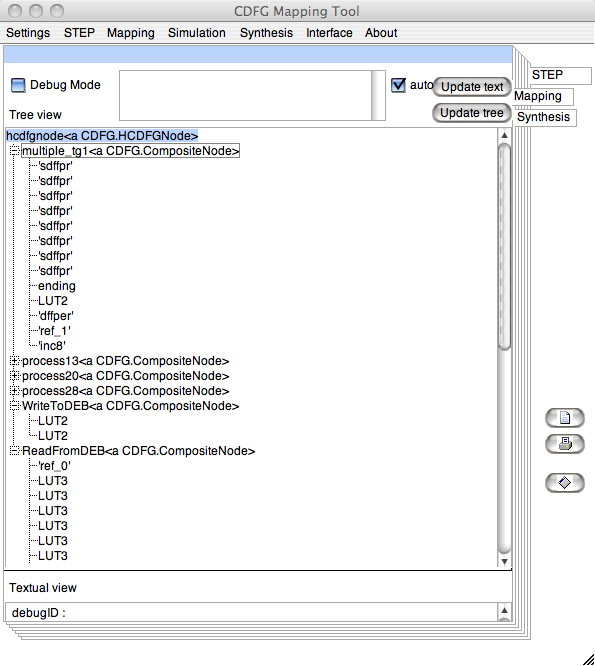

Biniou supports both library gifted and naked eFPGA families. Interchange formats are CDFGs as reported here.

|

|

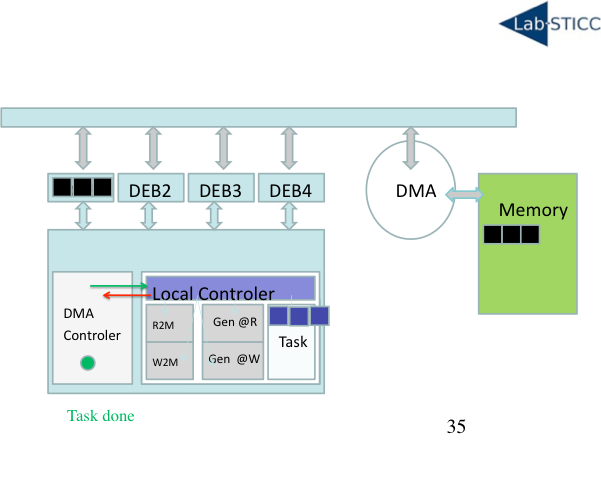

The synthesizer conforms to the protocol and the design the memory interface.

The hardware hypothesis behind this work is that every reconfigurable IP is provided a set of data exchange registers (DEB) on which the computation operates. The DMA is in charge of data moves, to dispatch data into DEBs depending on computation spatial organization and to grab back partial results into the main memory.

For fine grained architecture, two hierarchical controllers interact. The DMA controller synchronizes with the external irq/ack. The local controller schedules the computation.

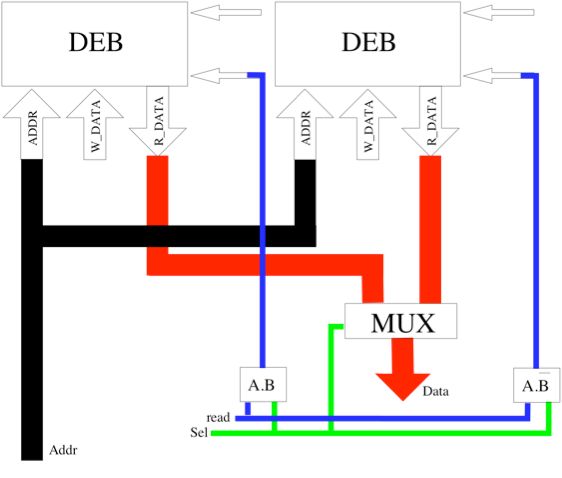

Read, Write, Read/Write access are supported as well as virtualization as shown by the following figure.

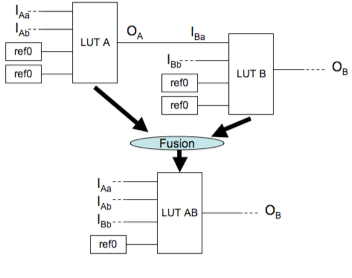

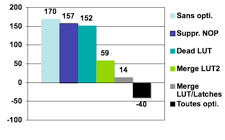

The fine grained architecture synthesizer output a verilog netlist. The optimizations (figure bellow left) on these netlists outperform vendor’s tools (figure below right)

|

|

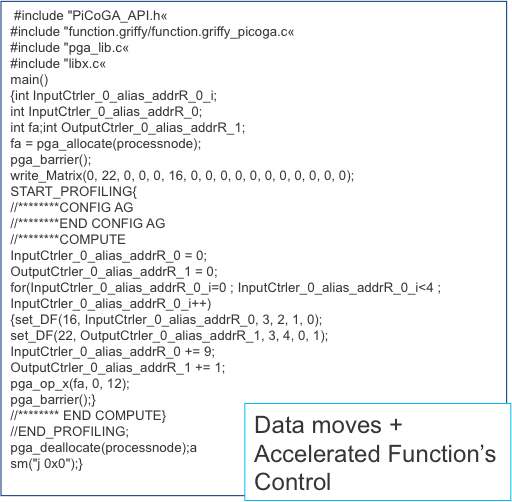

The Madeo+ DREAM synthesizer (credits: Damien Picard) produces both a C code to be further run on the processor and a griffy-C code to configure the matrix.

|

|

| QRisc code | HW configuration |

It is also possible to automate this architectural variation, and to collect feedback to drive the designer’s choices regarding a class of target application to implement.

Simple Example

|

|

Command Line example

|