Madeo

Madeo FET

The

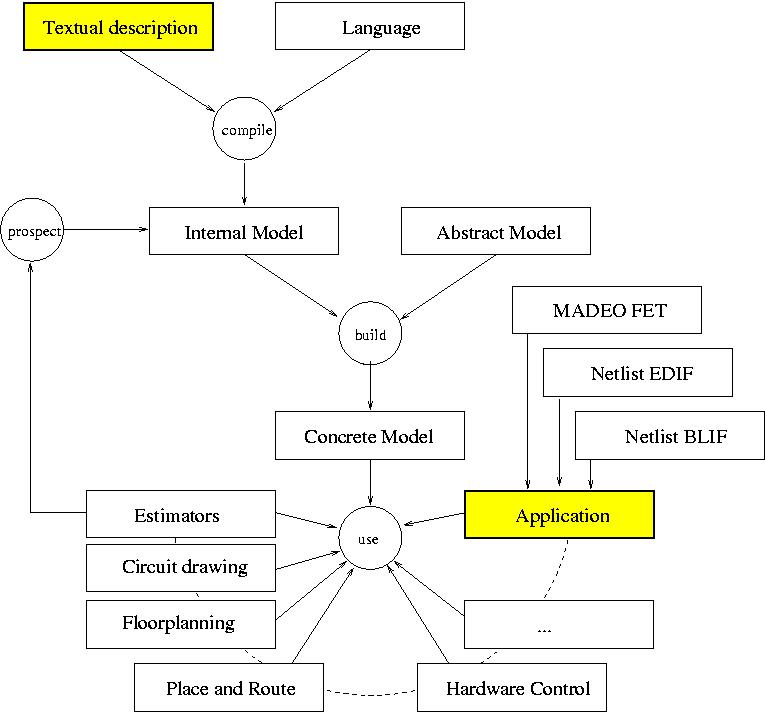

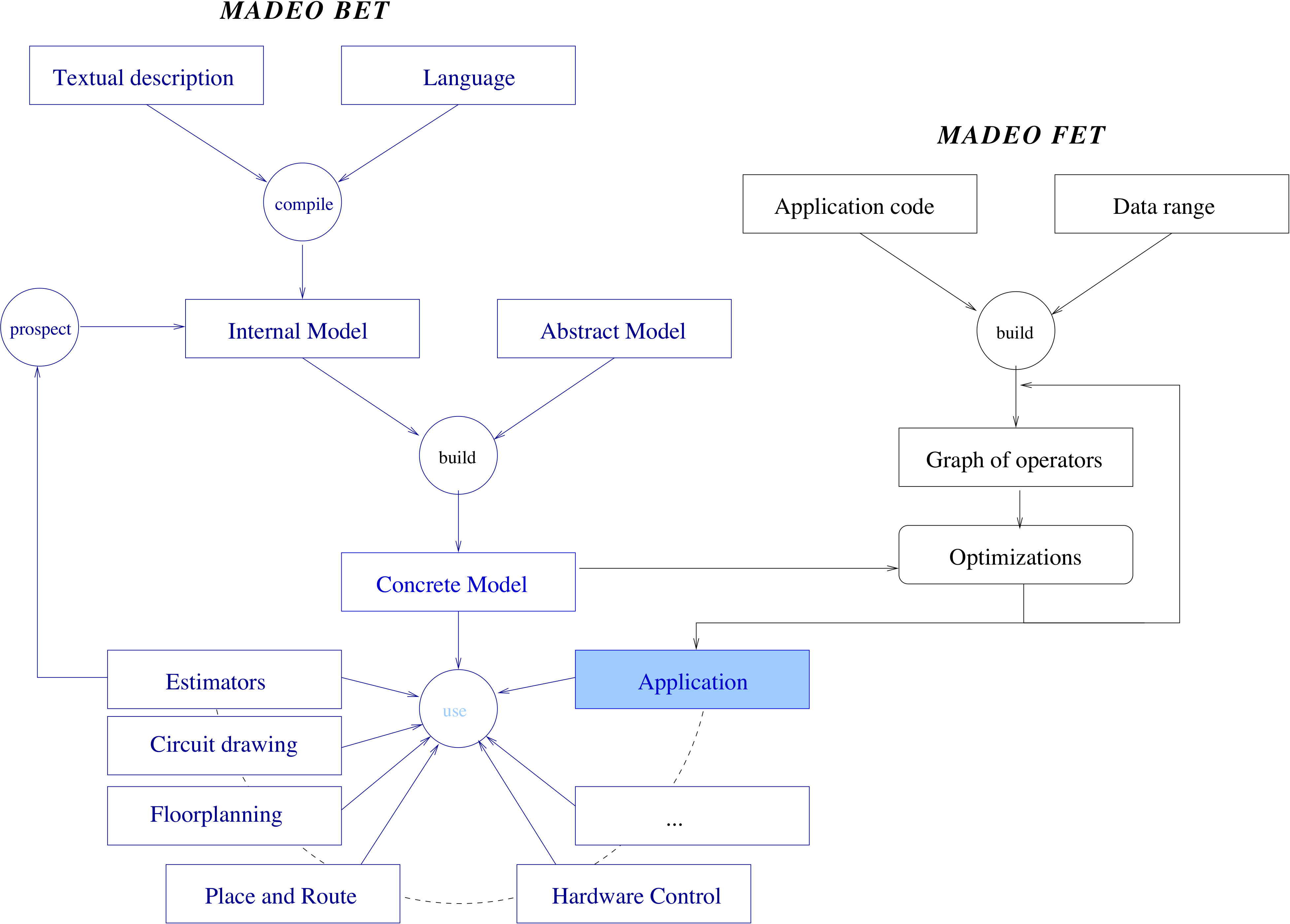

Madeo framework [bib]

[tutorial]

[flyer]

[doc]

is an open and extensible modeling environment that allows to

represent reconfigurable architectures. It acts as a one-stop

shopping point providing basic functionalities to the programmer

(place&route, floorplaning, simulation, etc.).

|

Setting up libraries of highly optimized operators is a time consuming task. Madeo-fet aims at decoupling behavioral specification from enumerated-types based contexts. The benefit is to support an automatic context-aware refactoring of operators. [bib].

|

A first consequence of this advantage is the restricted range of basic types coming from the capabilities of ALU/FPUs or memory address mechanisms. Control structures strictly oriented toward sequentiality are another aspect that can be criticized. As an example, programming for multimedia processor accelerators remains procedural in spite of all the experience available from the domain of data parallel languages. Hardware description languages have rich descriptive capabilities, however the necessity to use libraries has led the language designers to restrict their primitives to a level similar to C.

Textual editor

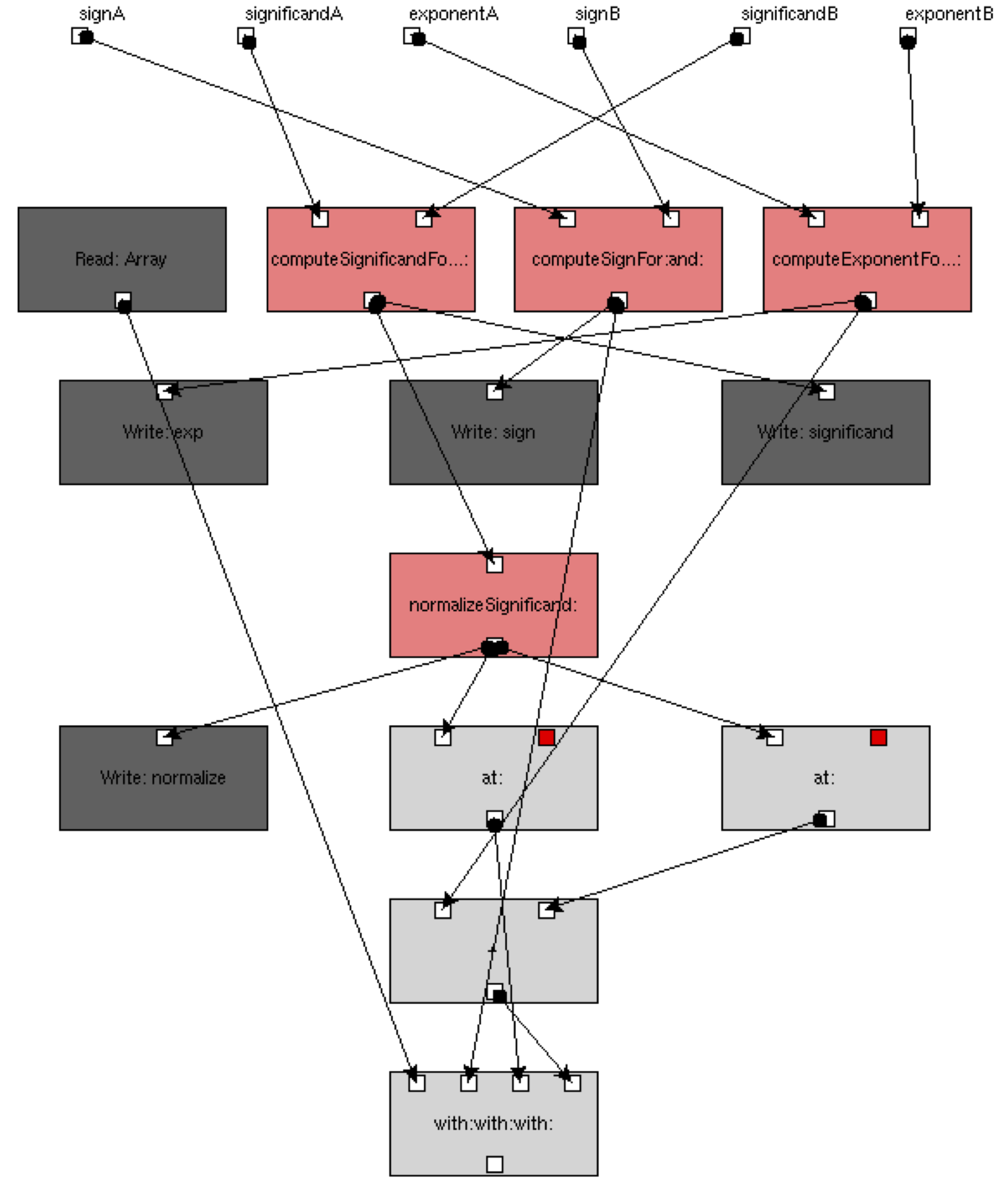

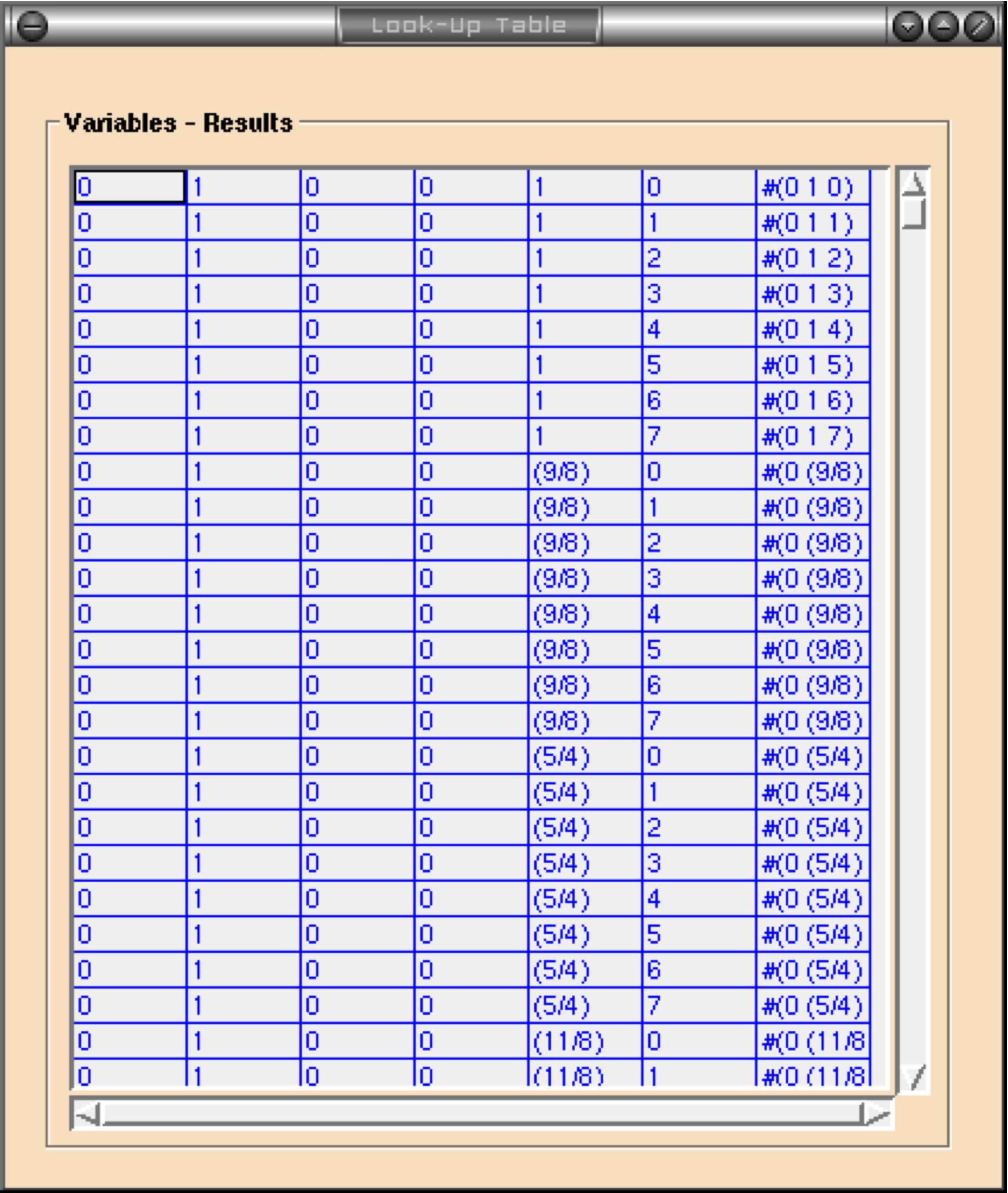

(1) Floating point multiplication

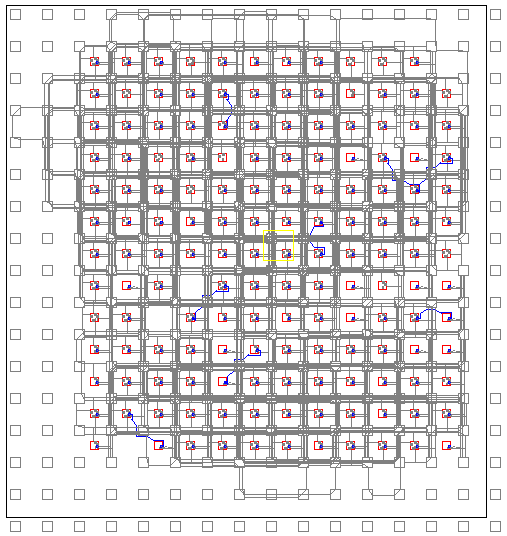

The

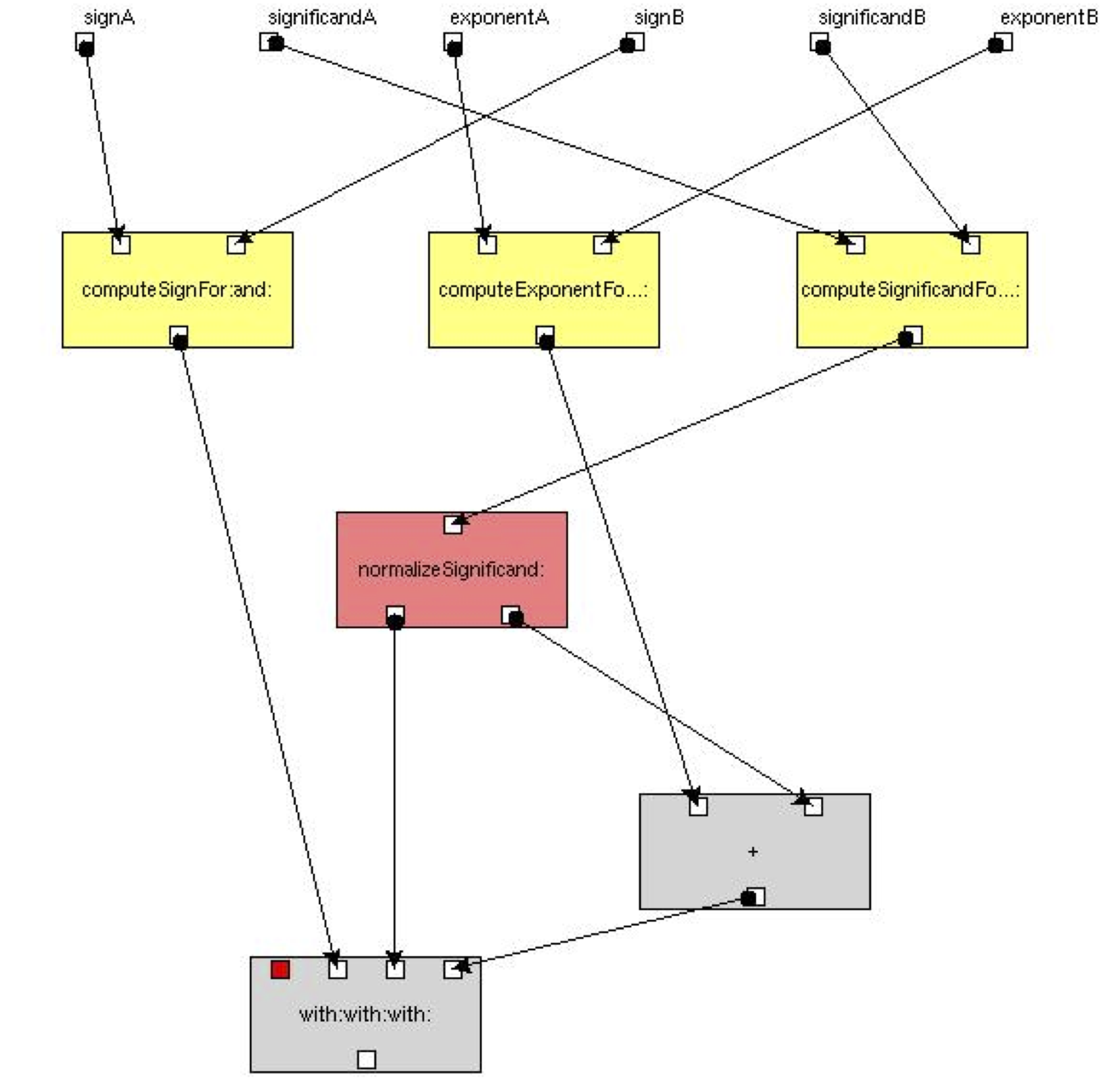

resulting graph is converted into logic by calling SIS.Yellow

nodes are hierarchical ones, red nodes are atomic ones, red inputs

are litterals (in this case, ArrayedResult class). The

normalize:significand: node has been refactored and outputs two

values: (value + offet).

(2) Context aware optimization of (1)

(3) High level LUT representation of computations

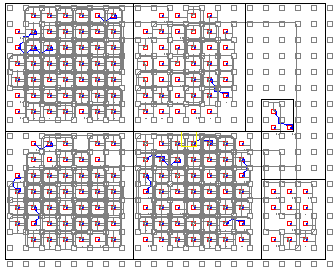

Madeo

offers a schematic view in addition to high level code based

representation.

The application can be automatically implemented on reconfigurable

architectures using MADEO-Fet,

as illustrated by (4) and (5).

application context.