DRAGE

Context

[Damien Picard's PhD thesis]Reconfigurable Computing (RC) aims to use

the flexibility of the configurable logic proposed by FPGA

components to enhance computation performance. The common idea is

that RC fills the gap between a general purpose

Von Neumann architecture (microprocessor) and a highly specific

full custom architecture (ASIC -

application specific integrated circuit) by programming an

appropriate architecture.

Microprocessor performances are limited by the

sequential behavior while ASICs suffer the

definitive silicon implementation. FPGA components appear as a

trade off between these two alternatives: a same physical support can be

re-programmed (or reconfigured) to support any suitable

architectures. Hence, reconfigurable computing claims to add both

the flexibility of the programming machines and

the speed of specific architectures.

The reality is not so obvious. First, an FPGA

architecture is much slower than its ASIC

counterpart. This is mainly due to

its programmable nature, which requires

signals to pass along many programmable

electronic switches, compared to a direct silicon

implementation.

Coarse grained architectures reduce this effect by sizing up logical

grain.

Second, the synthesis of a specific architecture onto a FPGA component

is still a long and error-prone process that remains far to

be completely automated. The architecture to implement

is often specified in VHDL, and requires a

lot of simulation steps to be validated.

In addition, a design designed

with a particular reconfigurable platform in mind sticks to this

target and exhibits poor re-use: the portability between different

configurable platforms is not ensured due to the lack

of programming model.

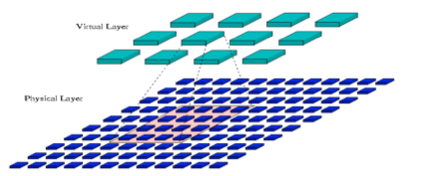

A way for increasing flexibility is to define a virtual FPGA

structure. In that case, an architecture is not

defined relatively to a specific FPGA component,

but relatively to a virtual FPGA structure

which will be implemented across the different

existing platforms and across their next generations.

|

Virtual FPGA is a concept that was first introduced in Placing,

Routing, and Editing Virtual FPGAs [Ref] |

As for virtual machine, such as the JVM (Java

Virtual Machine), we must deal with the loss

of performance introduced by the virtual layer. In our

case a virtual structure will have a limited amount of resources

(virtual logic blocks) and the clock speed will be slowed

down compared to a real FPGA

component. To keep performance reasonable

one could specialize the virtual structure toward

a specific field of applications. In that case,

integrating into the virtual level domain specific functions

could balance the extra-cost.

If designing a range of specialized virtual FPGA structures

targeted to various application

domains will guarantee a

minimum of performance, one has to

wonder how these architectures will be

programmed. More precisely, the problem is to

get the appropriate

utility programming tools, such as, for example, the

place-and-route step, for each specialized FPGA structure

developed. Of course, we cannot imagine to rewrite

from scratch another set of tools each time a new FPGA structure

is proposed.

DRAGE

Next figure shows a simple example of PicoGA inspired architecture. IOs are located on the left side. Computations are organized as rows, with registers and multiplexers based connections between rows. Used resources appear as blue lines (wires) and red boxes (ALUs).

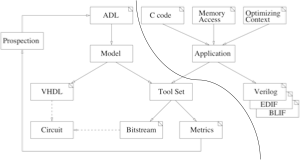

Next figure illustrates the flow. Only the left side makes sense here. The process starts from a ADL description of the target from which we derive (MDE approach) a custom tool suite and a VHDL description of the target supporting multi context and partial/dynamic reconfiguration.

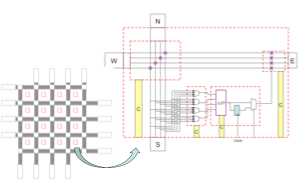

A simple mesh architecture appears as a matrix of basic cells embedding a switch bloc and a LUT.

The full description is automatically computed to simplify border

cells.

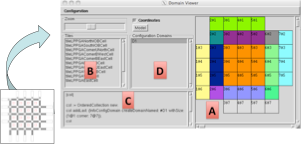

A configuration manager is provided. Several options can be activated

such as adding several configuration layers for configuration

pre-fetching.

The bistream structure conforms to the reconfiguration page granularity the designer has chosen.

A layout with a microblaze supporting a Coarse Grained Reconfigurable Architecture extension.