Nano Madeo

Madeo BET

The

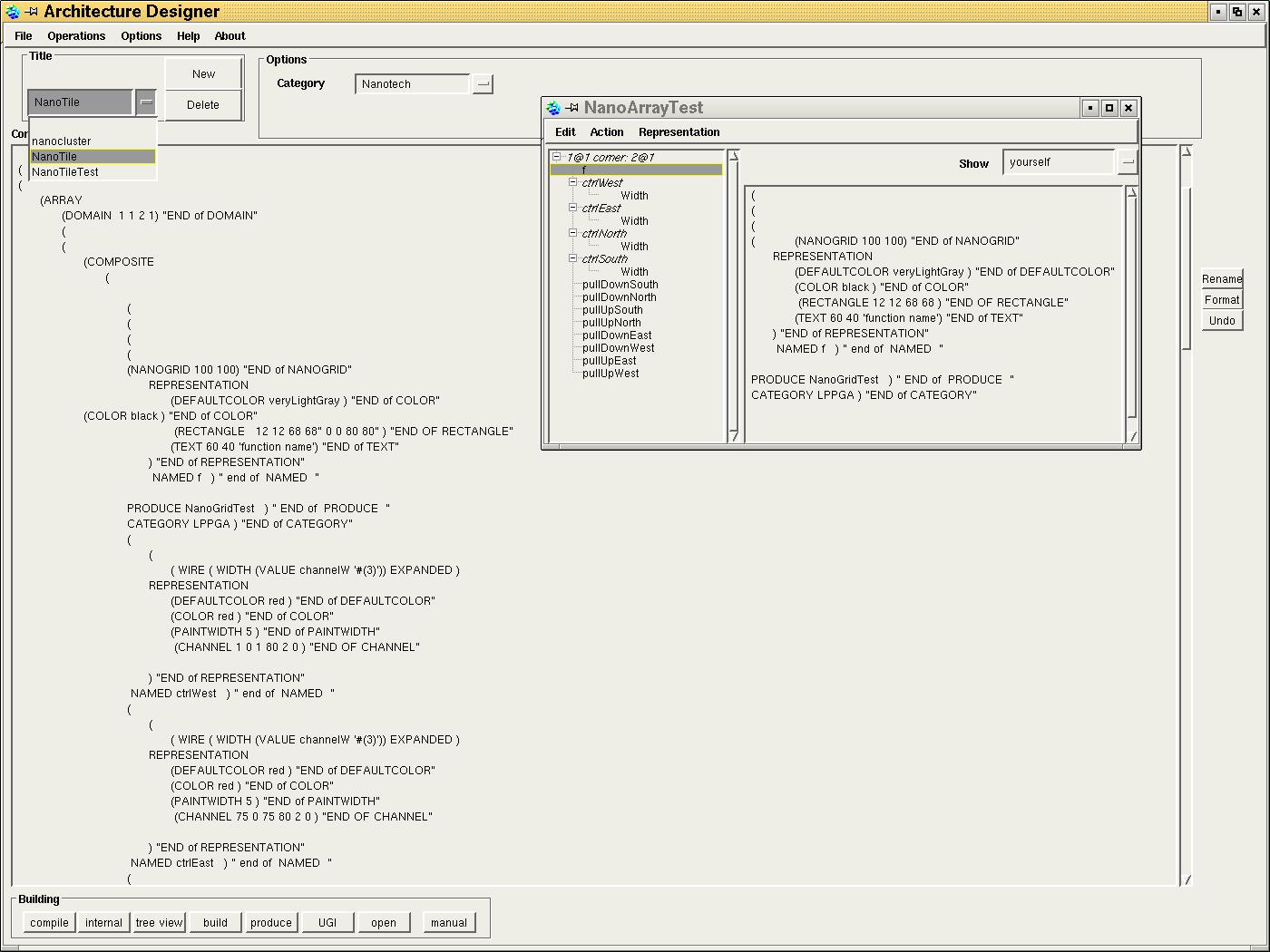

Madeo framework [bib]

[tutorial]

[flyer]

[doc]

is an open and extensible modeling environment that allows to

represent reconfigurable architectures. It acts as a one-stop shopping

point providing basic functionalities to the programmer

(place&route, floorplaning, simulation, etc.).

Madeo for Emerging technologies

Madeo has been extended to support mixed micro-nano architectures.

The underlying hardware hypothesis come from Pr Moritz research at UMass.

This happens at two levels : first the model describing the target has been extented with new elements, secondly the synthesis layer has been refactored to output two levels logic with complementary signals. [bib] [bib-french].

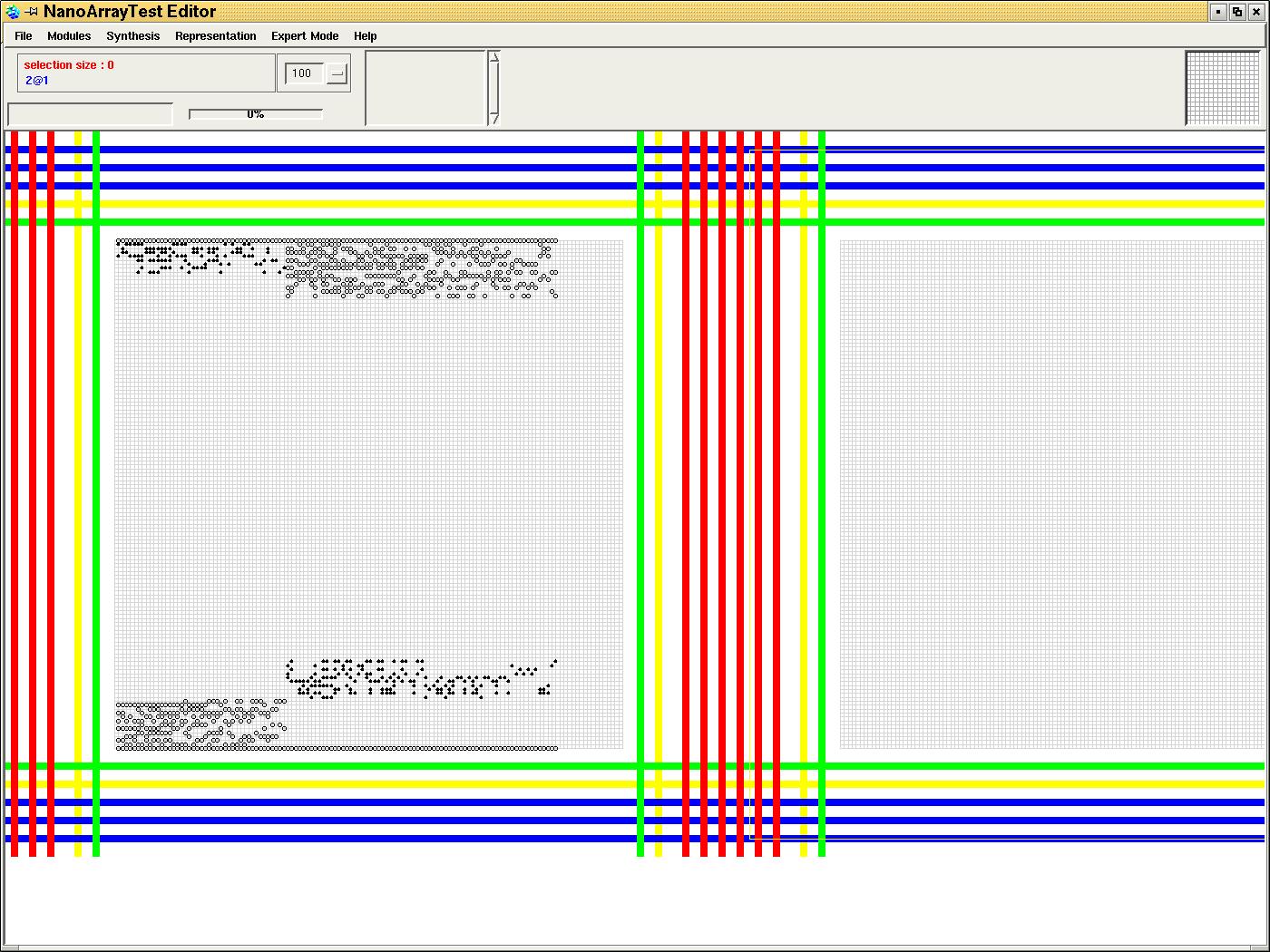

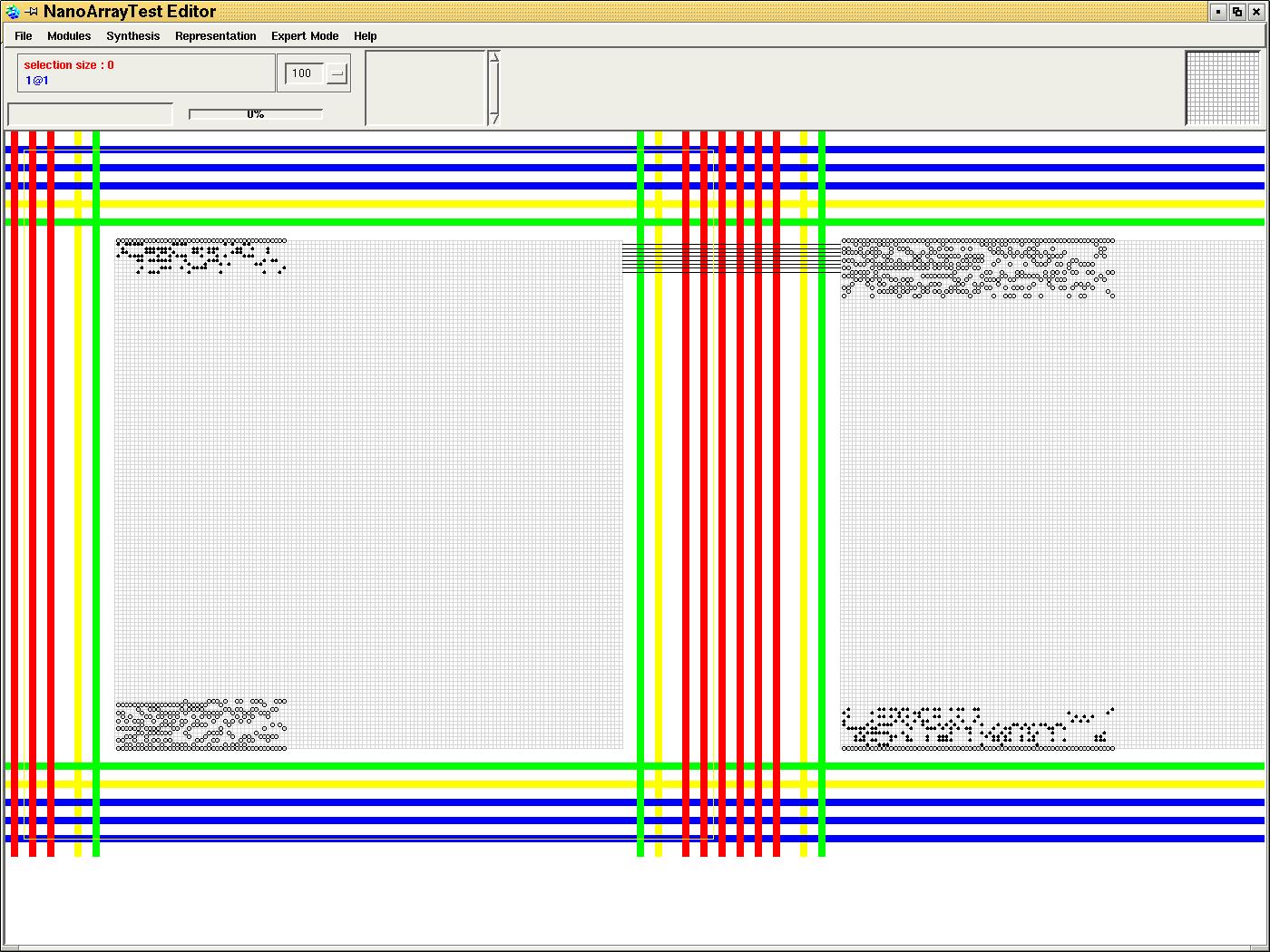

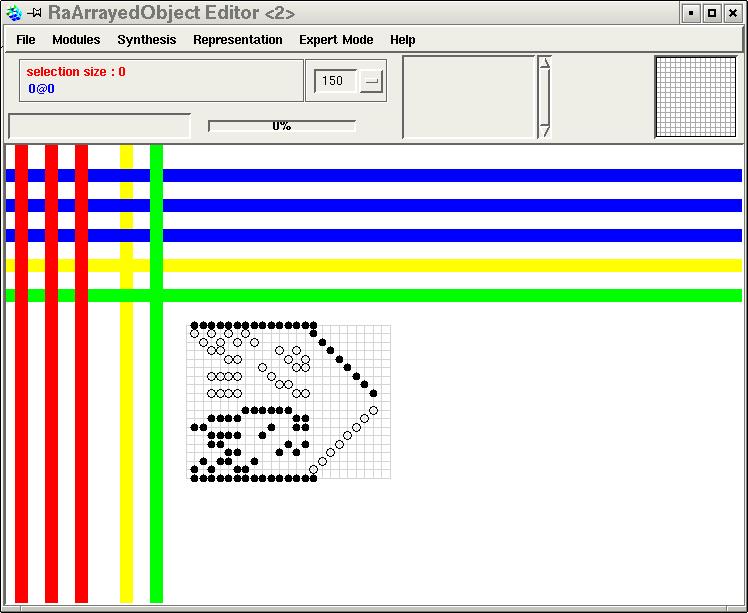

The tool flow has been revised to support several placing and routing policies. As an example, the figure below shows how atomic function calls are placed on a single tile whereas multiple operations are dispatched over several tiles (right).

|

|

| Implementing f(a,b,c) = a+ b +c | Implementing f(a,b,c) = (a+b) + c |

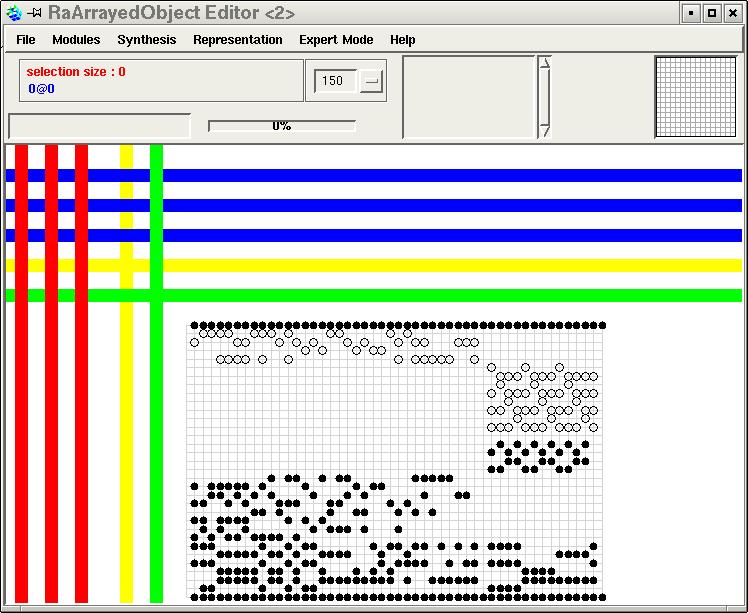

NanoMadeo has been validated by implementing the WISP (WIre Streaming Processor) processor. The two figures below illustrate the register file (hand made design on the left, automated design on the right). Using NanoMadeo some designs issueshave been detected then fixed. capability (right), such as sizing the bitwidth of operands and considering Galois Fields arithmetics instead of classical operators.

|

|

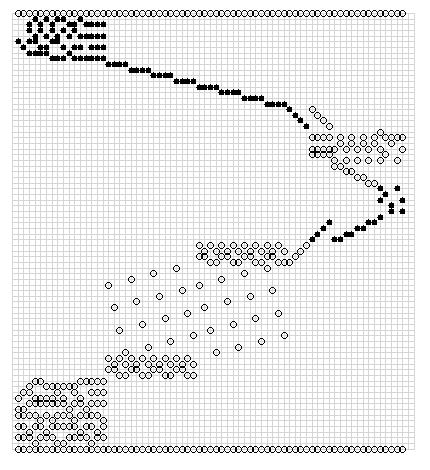

The two figures below illustrate the program counter (with the loop mechanism appearing as the two diagonals on the right) and a simple ALU.

|

|

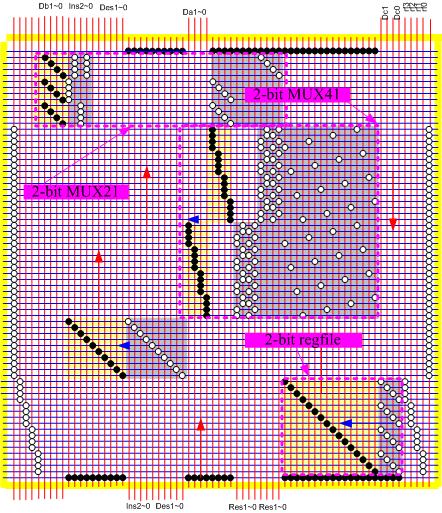

Madeo for Virtual FPGA on top of Emerging technologies

Madeo-FET has been used to specify the architecture.

Madeo for Virtual FPGA on top of Emerging technologies

NanoMadeo

was also used to offer a toolset for nano

reconfigurable computing.

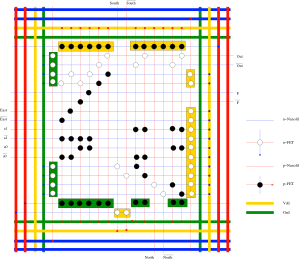

A template for FPGA on top of NASIC technology has been designed [Poungou's thesis]. This is directly connected to the virtual FPGA activity (Madeo-Bet, DRAGE, ARGEN).

|

Lut above CNT using Madeo |