## The Madeo framework

MADEO FET: Compiling for reconfigurable architectures MADEO BET: Generic backend tools for reconfigurable architectures

Loïc Lagadec

September 25, 2006

LESTER FRE 2734 ARCHITECTURES ET SYSTEMES Université de Bretagne Occidentale http://as.univ-brest.fr mail: loic.lagadec@univ-brest.Fr

## Contents

| Ι | $\mathbf{M}$ | ADEO BET                                     | 17        |

|---|--------------|----------------------------------------------|-----------|

| 1 | Sta          | rting guide                                  | 19        |

|   | 1.1          | Flow                                         | 19        |

|   | 1.2          | Installation (obsolete)                      | 21        |

| 2 | Des          | signing an architecture                      | <b>25</b> |

|   | 2.1          | Principles of design                         | 25        |

|   |              | 2.1.1 Method of design                       | 25        |

|   |              | 2.1.2 Hierarchical structure                 | 26        |

|   |              | 2.1.3 The atomic elements                    | 27        |

|   |              | 2.1.4 Accessing and connecting elements      | 31        |

|   |              | 2.1.5 Additional parameters                  | 33        |

|   | 2.2          | Using Architecture Designer                  | 36        |

|   |              | 2.2.1 Loading/Saving an architecture         | 36        |

|   |              | 2.2.2 Accessing/editing a description        | 38        |

|   |              | 2.2.3 Starting with a new description        | 39        |

|   |              | 2.2.4 Creating an architecture               | 39        |

|   |              | 2.2.5 Included examples                      | 40        |

|   |              | 2.2.6 Managing dependencies between elements | 40        |

|   | 2.3          | Generating documentation                     | 41        |

|   |              | 2.3.1 Principles                             | 41        |

|   |              | 2.3.2 Using MADEO-GENDOC                     | 41        |

|   | 2.4          | VHDL generation                              | 42        |

|   |              | 2.4.1 Principles                             | 45        |

|   |              | 2.4.2 Using VHDL Producer                    | 45        |

| 3 | Pro          | gramming an architecture                     | 47        |

|   | 3.1          | Introduction                                 | 47        |

|   | 3.2          | Towards new needs                            | 47        |

|   |              | 3.2.1 Algorithms                             | 47        |

| 4 | Too          | ols                                          | 49        |

|   | 4.1          | Using FPGA Editor                            | 49        |

|   |              | 4.1.1 Application description                | 50        |

|   |              | 4.1.2 Selecting BLIF/EDIF files              | 50        |

|   |              | 4.1.3 Placing and routing a BLIF/EDIF file   | 52        |

6 CONTENTS

|    |                 | 4.1.4 Pasting the module                              | 52 |

|----|-----------------|-------------------------------------------------------|----|

|    |                 | 4.1.5 Simulating the circuit                          | 56 |

|    |                 | 4.1.6 Using the window commands                       | 56 |

|    | 4.2             | Floor planning                                        | 57 |

|    | 4.3             |                                                       | 62 |

|    |                 | 4.3.1 Introduction                                    | 62 |

|    |                 | 4.3.2 Structural representation                       | 62 |

|    |                 |                                                       | 63 |

|    |                 | 1 0                                                   |    |

| 5  | $\mathbf{Arc}$  | nitectural prospection                                | 35 |

|    | 5.1             | Introduction                                          | 65 |

|    | 5.2             | Tools                                                 | 65 |

|    |                 | 5.2.1 Starting UIProspection                          | 65 |

|    |                 | 5.2.2 Analyzing an architecture                       | 65 |

|    |                 | 5.2.3 Selecting a BLIF/EDIF file                      | 66 |

|    |                 | _ ,                                                   | 67 |

|    |                 | v e                                                   | 68 |

|    |                 |                                                       | 69 |

|    |                 | oration retroiting one prospection to the transfer of |    |

|    |                 |                                                       |    |

| II | $\mathbf{M}$    | ADEO FET 7                                            | 73 |

| 6  | intr            | oduction                                              | 75 |

| -  | 6.1             |                                                       | 76 |

|    | 6.2             |                                                       | 78 |

|    |                 |                                                       |    |

| 7  | $\mathbf{desi}$ | gn flow and optimizations                             | 79 |

|    | 7.1             | design flow                                           | 79 |

|    | 7.2             | Possible Types                                        | 81 |

|    | 7.3             | v =                                                   | 81 |

|    |                 |                                                       | 81 |

|    |                 |                                                       | 85 |

|    |                 |                                                       | 85 |

|    |                 |                                                       | 85 |

|    |                 |                                                       | 86 |

|    |                 | •                                                     | 86 |

|    |                 | 1                                                     | 86 |

|    |                 | 1                                                     | 87 |

|    | 7.4             |                                                       | 87 |

|    | 1.4             |                                                       | 87 |

|    |                 | 0                                                     |    |

|    |                 |                                                       | 88 |

|    | 7 -             |                                                       | 89 |

|    | 7.5             | 1                                                     | 89 |

|    |                 | 1                                                     | 89 |

|    |                 | ·                                                     | 89 |

|    |                 | v                                                     | 89 |

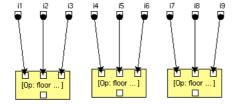

|    | 7.6             | the at: message                                       | QΩ |

CONTENTS 7

|    |      | 7.6.1 Comparisons                                         |    |    | 90  |

|----|------|-----------------------------------------------------------|----|----|-----|

| 8  | Gra  | phical tool                                               |    |    | 93  |

|    | 8.1  | Tool                                                      |    |    | 93  |

|    |      | 8.1.1 Control panel                                       |    |    | 93  |

|    |      | 8.1.2 The ToolBar                                         |    |    | 95  |

|    |      | 8.1.3 Code menu                                           |    |    | 96  |

|    |      | 8.1.4 Graphic representation                              |    |    | 98  |

|    | 8.2  | Interfacing low level tools (MADEO-bet)                   |    |    | 100 |

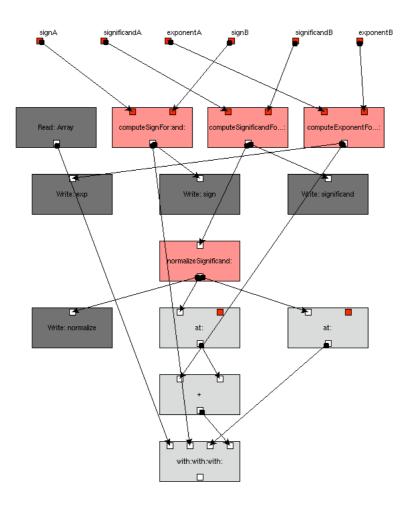

| 9  | Exa  | mple: Defining a floating point multiplier                |    |    | 101 |

|    | 9.1  | Introduction                                              |    |    | 101 |

|    | 9.2  | The implemented algorithm                                 |    |    |     |

|    | 9.3  | Implementation                                            |    |    |     |

|    |      | 9.3.1 The methods                                         |    |    |     |

|    |      | 9.3.2 The types                                           |    |    |     |

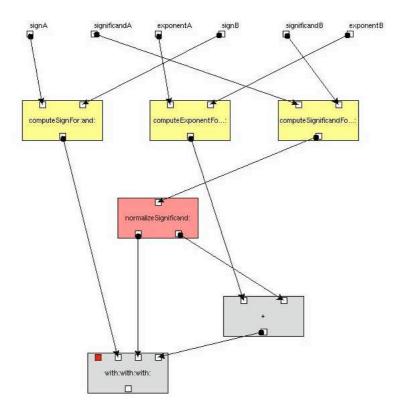

|    |      | 9.3.3 The resulting graph                                 |    |    |     |

|    |      | 9.3.4 Towards infinite precision operators                |    |    |     |

|    |      | 9.3.5 Conclusion                                          |    |    |     |

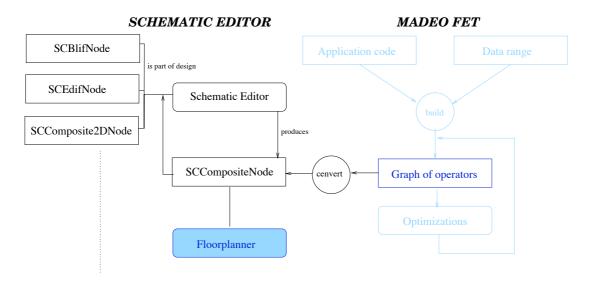

| 10 | Sche | ematic design                                             |    |    | 111 |

|    |      | Introduction                                              |    |    | 111 |

|    |      | Position within the flow                                  |    |    |     |

|    |      | Tool                                                      |    |    |     |

|    | 10.0 | 10.3.1 Example                                            |    |    |     |

|    |      | 10.3.2 Composite nodes and hierarchical visiting          |    |    |     |

|    |      | 10.3.3 Conclusion                                         |    |    |     |

|    |      |                                                           |    |    |     |

| II | I A  | ppendix                                                   |    |    | 117 |

| A  | MA   | DEO BET appendix                                          |    |    | 119 |

|    |      | Some examples of architectures description using the gr   | ar | n- | 110 |

|    |      | mar                                                       |    |    | 119 |

|    |      | A.1.1 First basic example                                 |    |    | 119 |

|    |      | A.1.2 Example 2                                           |    |    | 121 |

|    |      | A.1.3 Example 3                                           |    |    | 123 |

|    |      | A.1.4 Example 4 with custom representation                |    |    |     |

|    |      | A.1.5 LPPGA                                               |    |    |     |

|    | A.2  | Grammar                                                   |    |    | 130 |

|    | A.3  | Heterogeneous architectures                               |    |    |     |

|    | A.4  | Inspecting changes over the definition of an architecture |    |    |     |

|    | A.5  | Textual output                                            |    |    |     |

|    | A.6  | Changing the cost function of the placer                  |    |    |     |

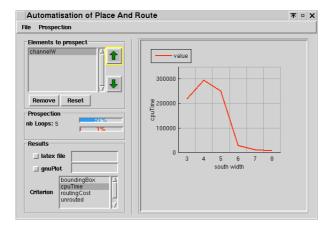

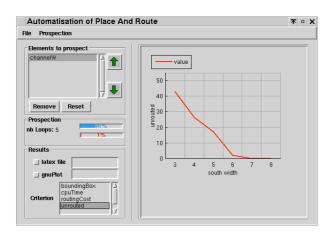

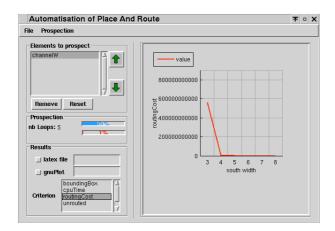

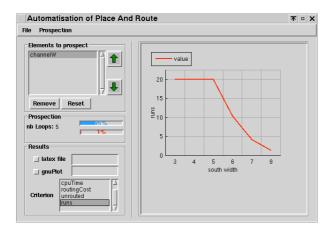

|    | A.7  | Prospection results                                       |    |    |     |

|    | A.8  | Example of prospection                                    |    |    |     |

|    |      | A.8.1 History of prospecting result                       |    |    | 142 |

8 CONTENTS

|              |      | A.8.2              | Average of prospecting result | 3 |

|--------------|------|--------------------|-------------------------------|---|

| В            | Gen  | Doc re             | esults 14                     | 5 |

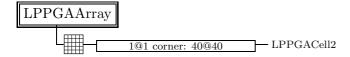

|              | B.1  | LPPG               | AArray                        | 7 |

|              |      | B.1.1              | Architecture Design (Level 1) | 7 |

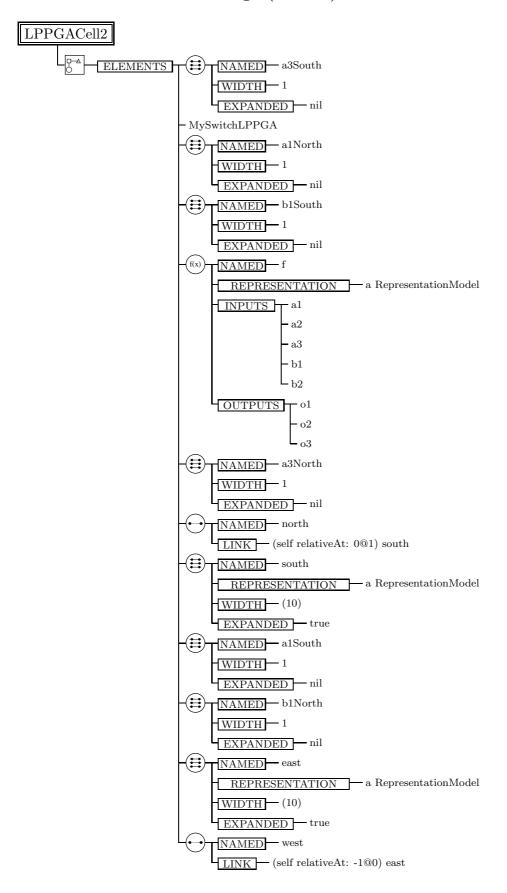

|              | B.2  |                    | ACell2                        |   |

|              |      |                    | Architecture Design (Level 2) |   |

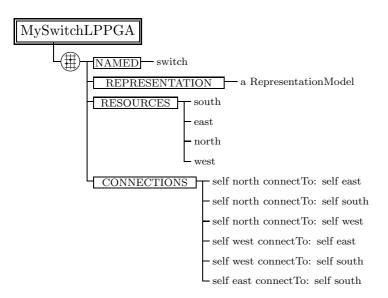

|              | B.3  |                    | tchLPPGA                      |   |

|              |      |                    | Architecture Design (Level 3) |   |

|              |      |                    | es                            |   |

|              |      |                    | Annexes 1: Sources LPPGACell2 |   |

| $\mathbf{C}$ | Mac  | deo fet            | appendix 15°                  | 7 |

|              |      |                    | Edif description              | 7 |

|              |      |                    | smalltalk code                |   |

|              |      |                    |                               |   |

|              |      |                    | Resulting Hierarchical Blif   |   |

|              | C.2  |                    | ing Flatten Blif              |   |

| D            | Sis  | $\mathbf{scripts}$ | 16'                           | 7 |

| ${f E}$      | Infe | rence              | 169                           | 9 |

|              | E.1  | CIR_M              | ethodGraph                    | 0 |

|              | E.2  |                    | lock                          |   |

|              | E.3  |                    | perator                       |   |

|              |      |                    |                               |   |

# List of examples

| 1.1  | Launching the environment                                    | 21 |

|------|--------------------------------------------------------------|----|

| 2.1  | The ARRAY syntax                                             | 26 |

| 2.2  | The COMPOSITE syntax                                         | 27 |

| 2.3  | The FUNCTION syntax with explicit naming                     | 28 |

| 2.4  | The FUNCTION syntax with global IOs                          | 28 |

| 2.5  | The WIRE syntax                                              | 29 |

| 2.6  | The REGISTER syntax                                          | 29 |

| 2.7  | The MULTIPLEXER syntax                                       | 30 |

| 2.8  | The SWITCHBLOCK syntax                                       | 30 |

| 2.9  | The REFERENCE syntax                                         | 31 |

| 2.10 | Naming the elements                                          | 31 |

| 2.11 | Accessing the elements                                       | 31 |

| 2.12 | The LINK syntax                                              | 32 |

| 2.13 | The LINK alternative syntax                                  | 32 |

| 2.14 | The CONNECTION syntax                                        | 32 |

| 2.15 | The alternative CONNECTION syntax                            | 33 |

| 2.16 | The PRODUCE syntax                                           | 33 |

| 2.17 | The CATEGORY syntax                                          | 34 |

| 2.18 | The REPRESENTATION syntax                                    | 34 |

| 2.19 | The custom parameters syntax                                 | 35 |

| 2.20 | The BASECOST syntax                                          | 36 |

| 4.1  | The floorplanner cost function                               | 59 |

| 4.2  | Setting the penalty                                          | 59 |

| 4.3  | First example                                                | 60 |

| 4.4  | Second example                                               | 60 |

| 4.5  | A serial adder                                               | 64 |

| 5.1  | Defining MV-variables                                        | 68 |

| 7.1  | Literals                                                     | 81 |

| 7.2  | Intervals                                                    | 81 |

| 7.3  | Radix based                                                  | 81 |

| 7.4  | Unions                                                       | 81 |

| 7.5  | GF16                                                         | 81 |

| 7.6  | GF128                                                        | 81 |

| 7.7  | Swapping the most/less significand four bits for an integer  |    |

|      | ranging from 0 to 63                                         | 88 |

| 7.10 | when comparing a value to a literal, the literal must be the |    |

|      | receiver                                                     | 90 |

10 LIST OF EXAMPLES

| 7.8  | Swapping the most/less significand four bits for an integer         |      |

|------|---------------------------------------------------------------------|------|

|      | ranging from 1 to 63                                                | 91   |

| 7.9  | end of the 7.8 example                                              | 92   |

| 9.1  | The entry point. Each float appears as three values: a sign,        |      |

|      | a significand, and an exponent                                      | 102  |

| 9.2  | The first operation over the exponents                              | 102  |

| 9.3  | The operations over the signs                                       | 102  |

| 9.4  | The full operation over the significands, ignoring the whished      |      |

|      | data width                                                          | 102  |

| 9.5  | The significand normalization implies to shift and trucate the      |      |

|      | value before returning it, but to answer as well the shift that     |      |

|      | was applied in order to carry that shift over the exponent valu     | e103 |

| 9.6  | First type                                                          | 103  |

| 9.7  | Second type                                                         | 104  |

| 9.8  | Third type, with its associated values, either fraction or float,   |      |

|      | ranging from 1 to 2 - $\epsilon$ with $\epsilon = 2^{-3}$           | 104  |

| 9.9  | The Blif description of the 9.4 table enlights two caracteristics   |      |

|      | of the node: first, the $R_{out}(op)$ reduction factor is important |      |

|      | as the inputs are encoded using 6 bits and the outputs only         |      |

|      | require 4 bits, and secondily the outputs are called t39_13         |      |

|      | and $t40$ , what means the nodes owns two outputs, the first of     |      |

|      | which requires 3 bits and the other one only one bit                | 104  |

| 10.1 | The equation description of the adder                               |      |

| 10.2 |                                                                     |      |

| A.1  | An heterogeneous architecture                                       |      |

| A.2  | The <b>new</b> method generated from A.1                            |      |

| A.3  | Placement information                                               |      |

| A.4  | Routing information                                                 |      |

| A.5  | Example of cost function                                            |      |

| D.1  | The 5lut.script doing the technology mapping for 5-Luts             |      |

| E.1  | the $infereTypes$ method                                            | 170  |

| E.2  | The $infereOutputsType$ method                                      | 170  |

| E.3  | the $infereType$ method                                             | 171  |

| E.4  | the $infereTypes$ method                                            |      |

| E.5  | the $infereOutputsTypes$ method                                     |      |

| E.6  | The $infereOutputsTypes$ method                                     | 173  |

# List of Figures

| 1.1  | MADEO BET flow                                             | 20              |

|------|------------------------------------------------------------|-----------------|

| 1.2  | Snapshot of the common environment                         | 22              |

| 1.3  | Snapshot after the installation process has completed      | 22              |

| 1.4  | Saving your image                                          | 23              |

| 1.5  | Smalltalk menu                                             | 23              |

| 1.6  | Architecture Designer                                      | 23              |

| 2.1  | Principles of design                                       | 26              |

| 2.1  | View of the functions IOs connections                      | $\frac{20}{27}$ |

| 2.3  | Global view of the model                                   | 28              |

|      |                                                            | 29              |

| 2.4  | Example of action zone of wire                             |                 |

| 2.5  | Two examples of switches                                   | 30              |

| 2.6  | Some examples of the default user interface over the basic | 25              |

| 0.7  | elements of he architecture                                | $\frac{35}{37}$ |

| 2.7  | Loading an architecture description (1)                    |                 |

| 2.8  | Loading an architecture description (2)                    | 37              |

| 2.9  | Selecting a description                                    | 38              |

|      | Choosing a category                                        | 38              |

|      | Code generated by build                                    | 39              |

|      | The tree representation of a composite                     | 41              |

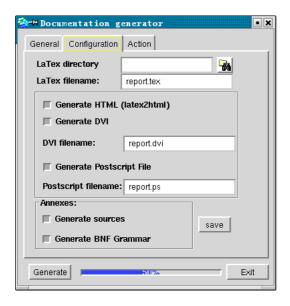

|      | The GenDoc user interface                                  | 42              |

|      | The GenDoc parameters                                      | 43              |

|      | The GenDoc actions                                         | 43              |

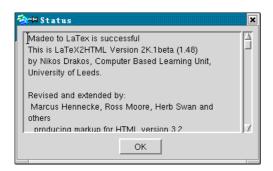

|      | The GenDoc transcript                                      | 44              |

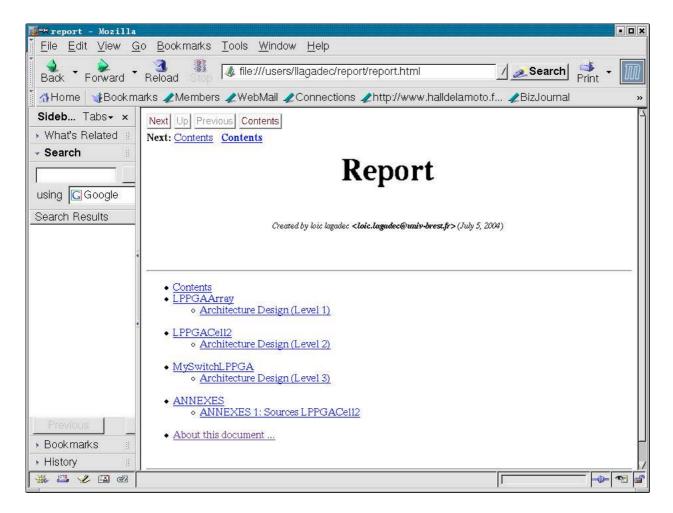

| 2.17 | The GenDoc html output                                     | 44              |

| 4.1  | The interface of FPGA Editor                               | 49              |

| 4.2  | The application description formalism                      | 50              |

| 4.3  | Selecting a BLIF/EDIF file from the menu                   | 51              |

| 4.4  | BLIF/EDIF File Browser                                     | 51              |

| 4.5  | selecting a BLIF/EDIF file                                 | 52              |

| 4.6  | The list of available modules                              | 52              |

| 4.7  | Pasting the module on the FPGA                             | 53              |

| 4.8  | After pasting the module on the FPGA                       | 54              |

| 4.9  | Selecting the zoom factor                                  | 54              |

| 4.10 | Representing either all or only used resources             |                 |

| 1 11                                          |                                                                                                                                                                           |                                  |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 4.11                                          | The simulation of P&R circuits                                                                                                                                            | 56                               |

| 4.12                                          | Floorplanning 1                                                                                                                                                           | 58                               |

| 4.13                                          | Floorplanning 2                                                                                                                                                           | 58                               |

| 4.14                                          | Floorplanning 3                                                                                                                                                           | 60                               |

|                                               |                                                                                                                                                                           | 61                               |

|                                               |                                                                                                                                                                           | 62                               |

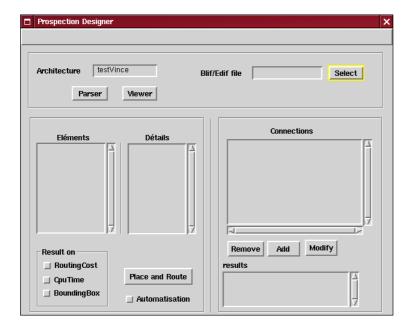

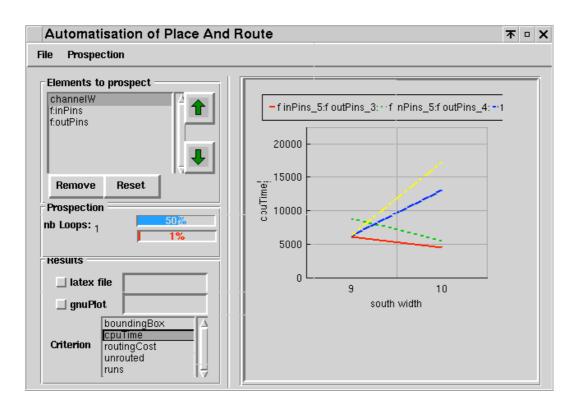

| 5.1                                           | Launching UIProspection                                                                                                                                                   | 66                               |

| 5.2                                           | Prospection Designer                                                                                                                                                      | 66                               |

| 5.3                                           |                                                                                                                                                                           | 67                               |

| 5.4                                           | Detailed view of the selected element                                                                                                                                     | 67                               |

| 5.5                                           |                                                                                                                                                                           | 68                               |

| 5.6                                           |                                                                                                                                                                           | 68                               |

| 5.8                                           |                                                                                                                                                                           | 68                               |

| 5.7                                           | 9 1                                                                                                                                                                       | 69                               |

| 5.9                                           |                                                                                                                                                                           | 70                               |

| 5.10                                          |                                                                                                                                                                           | 70                               |

|                                               |                                                                                                                                                                           | 71                               |

|                                               |                                                                                                                                                                           | 71                               |

| J.12                                          | Zacer suspect                                                                                                                                                             | • •                              |

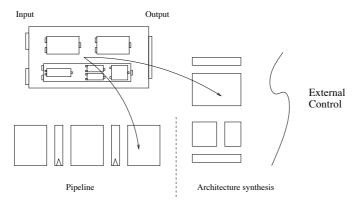

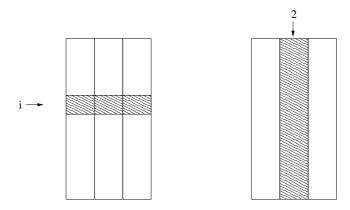

| 6.1                                           | The modules can be either flat or hierarchical; the modules                                                                                                               |                                  |

|                                               | can be composed in order to produce pipelines or can be in-                                                                                                               |                                  |

|                                               | stantiated during architecture synthesis                                                                                                                                  | 75                               |

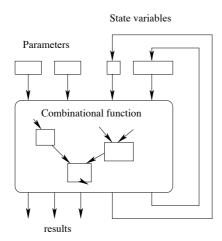

| 6.2                                           | State machines can be obtained by methods operating on pri-                                                                                                               |                                  |

|                                               | vate variables having known initial values                                                                                                                                | 76                               |

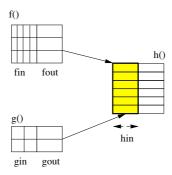

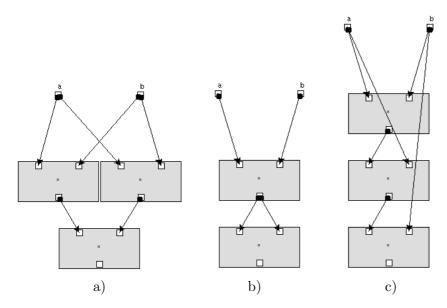

| 6.3                                           | Fan-in from 2 nodes with $Card(fout \times gout) < Card(fin) \times$                                                                                                      |                                  |

|                                               | Card(gin)                                                                                                                                                                 | 77                               |

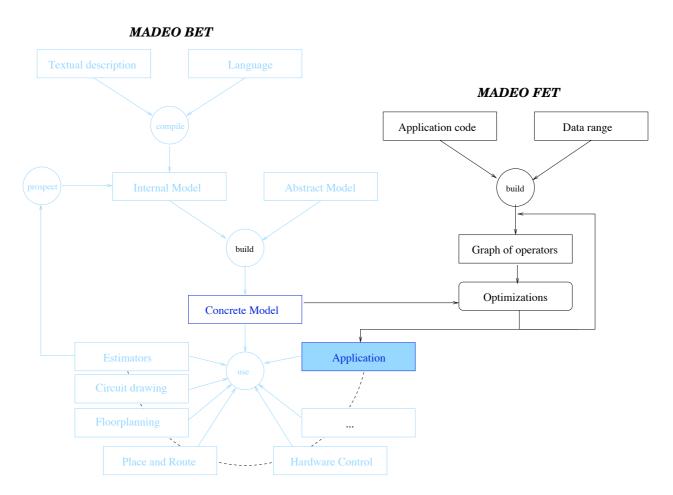

| 7.1                                           | MADEO BET and MADEO FET flow                                                                                                                                              | 80                               |

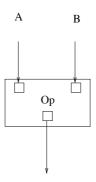

| 7.2                                           | A node links an output to some inputs, and computes the                                                                                                                   |                                  |

|                                               | output current value, depending on the inputs' current value                                                                                                              |                                  |

|                                               | in order to build the HL OO LUT                                                                                                                                           | 82                               |

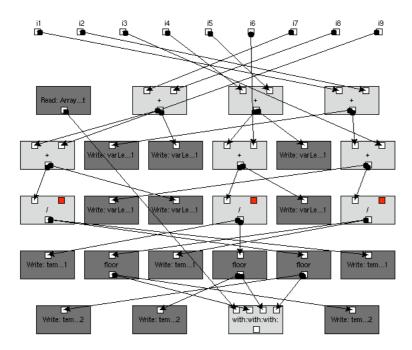

| 7.3                                           |                                                                                                                                                                           |                                  |

|                                               | The starting code encapsulating an ArrayedResult. Note that                                                                                                               |                                  |

|                                               | The starting code encapsulating an ArrayedResult. Note that the code is structured automatically by extracting all nodes                                                  |                                  |

|                                               | the code is structured automatically by extracting all nodes                                                                                                              | 84                               |

| 7.4                                           | the code is structured automatically by extracting all nodes                                                                                                              | 84                               |

| 7.4                                           | the code is structured automatically by extracting all nodes that belong to the inheritance tree of the values After the rewriting process, only three nodes remain. Note |                                  |

|                                               | the code is structured automatically by extracting all nodes that belong to the inheritance tree of the values                                                            | 84                               |

| 7.5                                           | the code is structured automatically by extracting all nodes that belong to the inheritance tree of the values                                                            | 84<br>86                         |

| 7.6                                           | that belong to the inheritance tree of the values                                                                                                                         | 84<br>86<br>90                   |

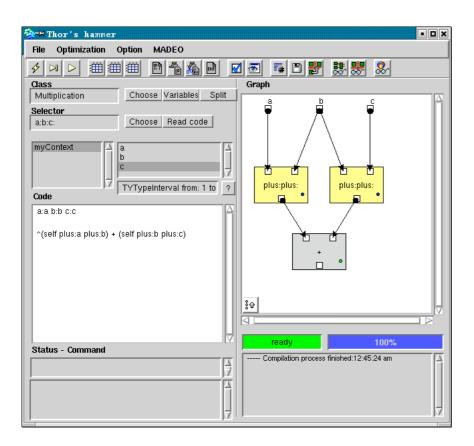

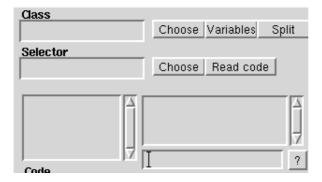

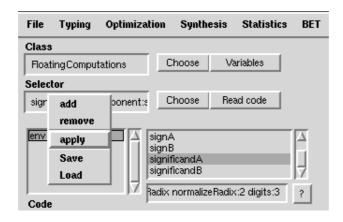

| 7.5<br>7.6<br>8.1                             | the code is structured automatically by extracting all nodes that belong to the inheritance tree of the values                                                            | 84<br>84<br>86<br>90<br>93<br>94 |

| 7.5<br>7.6<br>8.1<br>8.2                      | the code is structured automatically by extracting all nodes that belong to the inheritance tree of the values                                                            | 84<br>86<br>90<br>93<br>94       |

| 7.5<br>7.6<br>8.1<br>8.2<br>8.3               | the code is structured automatically by extracting all nodes that belong to the inheritance tree of the values                                                            | 84<br>86<br>90<br>93<br>94<br>94 |

| 7.5<br>7.6<br>8.1<br>8.2<br>8.3<br>8.4        | the code is structured automatically by extracting all nodes that belong to the inheritance tree of the values                                                            | 84<br>86<br>90<br>93<br>94<br>94 |

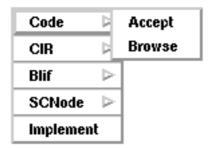

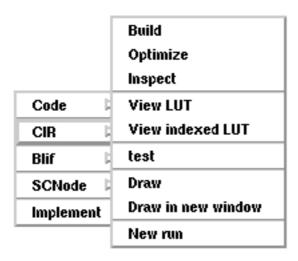

| 7.5<br>7.6<br>8.1<br>8.2<br>8.3<br>8.4<br>8.5 | the code is structured automatically by extracting all nodes that belong to the inheritance tree of the values                                                            | 84<br>86<br>90                   |

| 7.5<br>7.6<br>8.1                             | the code is structured automatically by extracting all nodes that belong to the inheritance tree of the values                                                            | 84<br>86<br>90<br>93<br>94<br>95 |

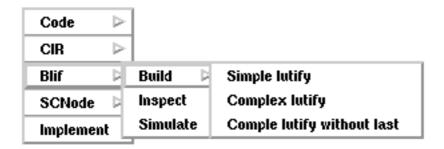

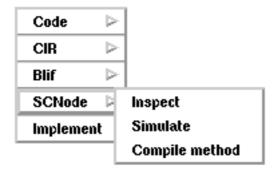

| 8.8  | BLIF menu                                          |

|------|----------------------------------------------------|

| 8.9  | SCNode menu                                        |

| 8.10 | The graph representation                           |

|      | MADEO FET - MADEO BET interfacing 100              |

|      |                                                    |

| 9.1  | A small floating Point multiplier                  |

| 9.2  | The reduced 9.1 graph                              |

| 9.3  | The 9.2 graph with operator fusion                 |

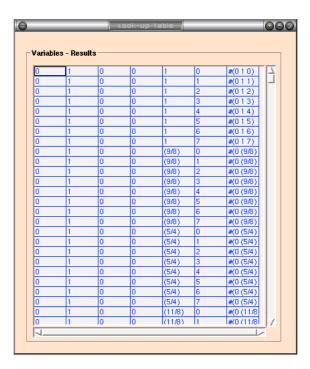

| 9.4  | The LUT of the normalizeSignificand: operator 108  |

| 9.5  | The global LUT                                     |

| 9.6  | Verification over the circuit                      |

| 10 1 | Interfacing MADEO-FET and the schematic editor 111 |

|      | The Schematic Editor launching procedure           |

|      |                                                    |

|      | The schematic editor                               |

|      | The SCNode Chooser                                 |

| 10.5 | Flattening nodes                                   |

| A.1  | Architecture viewer                                |

| A.2  | Analyzing the bounding box                         |

| A.3  | Analyzing the CPU time                             |

| A.4  | Analyzing the number of unrouted signals 140       |

| A.5  | Analyzing the routing cost                         |

| A.6  | Analyzing the number of runs (20 max) 140          |

| A.7  |                                                    |

|      | v C                                                |

## Introduction

**Reconfigurable architectures** offer a promising trade-off between the ASICs' peek performances and the flexibility the software ingeneers are used to. Their "tunable" nature widens their use scope, allowing to recoup the non recurning costs and makes them financially attractive.

Unfortunately, these architectures often suffer from a poor development environment preventing short time to market, and slowing down hardware evolutions.

From our point of view the two major points that diserve RA are:

- First, the application designing front end does not fully exploit the hardware capabilities; this is mainly due to the VLSI CAD domain from which emmerged the RA CAD nearly twenty years ago. A consequence is that applications are commonly described as VHDL programs that make use of C-like typed operators (8,16,32 bits operators) that are present in libraries despites the hardware permits to implement custom operators, with better performances.

- Secondly, the back end tools, that are needed to program such architectures, are strongly linked to their target architecture, exhibit poor reuse and bring a long development process for each new architecture. This prevents the designers from testing their architectures at an early stage, prior to any physical realisation, as these tools are the only solution to get an accurate feed back over a design choice. In addition, linking CAD tools to an architectural model makes architectures comparisons harder, and increazes the propability of defective software whereas resuse speeds up the development process, increazes producitvity and software quality.

The fact is that by keeping secret the technical informations the CAD tools designers need, the FPGAS vendors refuse third parties to bring up their own tools.

The Madeo project is an attempt to answer to these limitations. This project has been on since 95/96 and came after the ArMen project. One of the concluding remarks of the ArMen project was that to be dependent of the CAD tools the FPGAs vendors provide is highly time consuming as no API is preserved from one generation to another. Another conclusion was that programming a complex hardware mixing several computational

models requires a high level unified front end making use of code generation on demand. As a consequence, MADEO makes use of a non-typed functional language when designing application, and prohibits any commercial backend tools; MADEO is made of two layers, as introduced below:

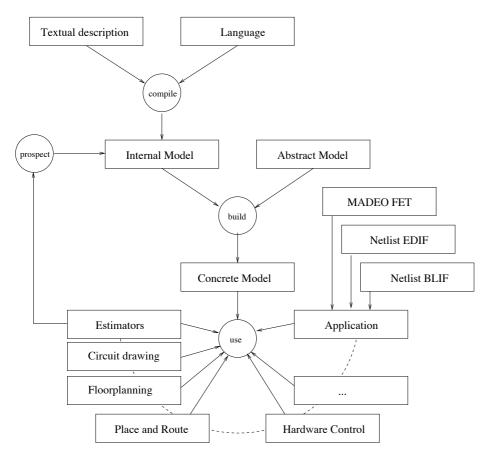

The top layer called MADEO-FET produces RTL logic or EDIF netlist, from a functional code (with no types) from one hand, and a context from another hand. A context describes the set of different values for every variable. By performing types inference, and several more classical optimizations, the compilation process results in a hierarchical graph of operations each of which owns a minimized logic description.

Implementing this graph cannot be archived based on library based operators. On the contrary, this stage requires to be able to produce custom operators, before composing them. This is done by invocating the back end layer.

The back-end layer called MADEO-BET produces a textual "bitstream" from a hierarchical RTL description (BLIF, EDIF, or an internal format supporting regular circuits) from one hand, and a modelization of an architecture from another hand. The designer benefits from a set of hardware elements (functions, switch, multiplexers, etc...) that can be combined and/or specialized to describe a given architecture. This stage is archived through a compilation process, after the designer has described within a private language its architecture.

A set of generic tools (P&R, floorplanner, regular editor, etc...) manipulates this architecture, with as main benefits, the capability to describe any architecture and to do it fast, to share the tools between all these architectures, and to get feedback over architectures.

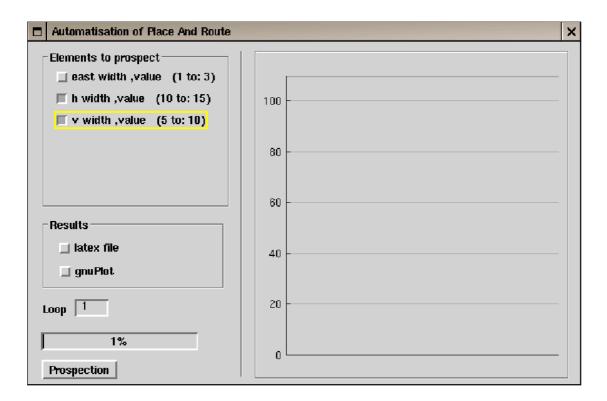

It is also possible to automate this architectural variation, and to collect feedback to drive the designer's choices regarding a class of target application to implement.

VHDL descriptions are to be added to offer the designer a way to go up to the physical synthesis of its architecture. This will benefits as well to the tools by returning after-synthesis accurate information to tune the algorithms parameters.

**This report** introduces the MADEO framework from a user point of view, starting with MADEO-BET (chapters 2 to 5) and considering MADEO-FET as a second part.

The first chapter is a short starting guide through the installation procedure.

# Part I MADEO BET

## Chapter 1

## Starting guide

#### Introduction

MADEO-bet[7] [8] [6] is a framework composed of a set of back-end tools for modeling and programming reconfigurable architectures. MADEO-bet comes within the framework of a more general set of tools, targeting the programming and the manipulation of reconfigurable architectures at a very high level of abstraction, using a symbolic and non-typed environment. MADEO-bet provides the generic back-end in this compilation flow.

This chapter does not introduce the upper stages of MADEO which are described in part II, but focuses on practical information regarding the backend tools. This report is splited into several sections: the first one describes the installation procedure. The second section introduces the modelization stage while the next section describes its associated tool: the *Architecture Designer*. The next chapter details the way to program a architecture while the following one addresses the tool allowing to program a modelized architecture, including floorplanner and regular circuit editor. The last chapter details how to automate the architectural prospection in front of a fixed circuit.

#### 1.1 Flow

CAD tools for reconfigurable architectures commonly suffer from several lacks. First, except few tools such as VPR [2], they are dedicated to a single architecture, or at most to a family of architectures. It's a fact that taking advantage of a cad tool may prevent some bad decision when designing a new architecture. Designing an architecture meanwhile developing its associated cad tool can lead to serious problem as illustrated by the PROTEUS project [4].

Another point is that a tool which fits to any architecture, allows not simply testing the architecture, but more, allows comparing several architecture. And Last, by reusing most of the code, such a tool decreases the required amount of development time.

Secondly, CAD tools do not exhibit any feature that would allow to draw

Figure 1.1: MADEO BET flow

regular circuits, based on an existing application structuring. Designers claim the tools must bring new functionalities such as hot debugging by interfacing the real architecture if any, or supporting several abstraction levels that could be mixed or exchanged one to the other, or drawing regular circuits.

MADEO-BET focuses on these points; and provides a generic backbend tool that can adapt to any architecture, according this architecture is described within a custom language. In addition, by providing a stable and common back end to a higher level compiler, MADEO BET lets MADEO-FET benefit from accurate information when electing a design policy for an application both depending on the hardware and the application field (see part II).

#### 1.2 Installation (obsolete)

**Requirements** In this section, we assume that Visualworks [1] has been previously installed<sup>1</sup>. As well, we assume that all the files of the MADEO-bet package have been copied into a local user directory.

**The MADEO-bet package** The MADEO-bet package is composed of the following Visualworks files :

- MADEO-bet.pcl, madeo-bet.pst

- EDIF.pcl, EDIF.pst

- visualxx.im (where xx represents the Visualworks version number). the 30 version runs on windows, and the 31 version runs on Linux 2.2x kernels

- additional files such as some BLIF/EDIF files

These files are contained in an archive file name imagexx.tgz (where xx represents the Visualworks version number).

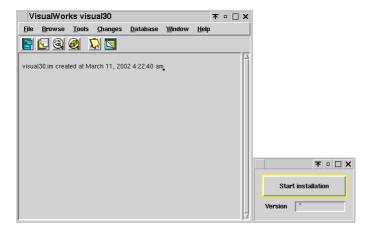

The installation The installation process starts with launching the Visualworks environment in a similar manner than the code provided in 1.1.

(VISUALWORKS)/bin/visualnc visualxx.im

Code Ex. 1.1: Launching the environment

Be careful of choosing as current directory the one in which the MADEO-bet files are present.

After this is done, the user' screen must be close to the one of figure 1.2. The upside windows is called VisualLauncher. Click then on the **start** installation button to install the package.

Figure 1.2: Snapshot of the common environment

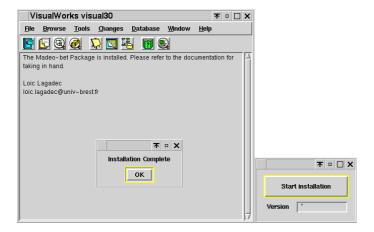

Figure 1.3: Snapshot after the installation process has completed

After the installation completes (figure 1.3), it is recommended to save the resulting image (figure 1.4).

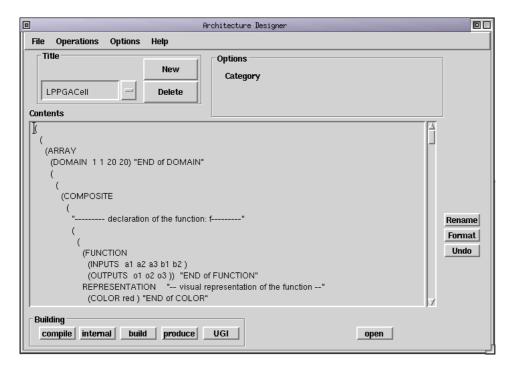

**Opening the graphical interface** Designing a new architecture relies on the *Architecture Designer* tool (figure 1.6) which is accessible through the last icon (figure 1.5).

The full description of the FPGA takes place in this interface.

<sup>&</sup>lt;sup>1</sup>To install Visualworks, refer to http://www.cincon.com

Figure 1.4: Saving your image

Figure 1.5: Smalltalk menu

Figure 1.6: Architecture Designer

## Chapter 2

## Designing an architecture

#### 2.1 Principles of design

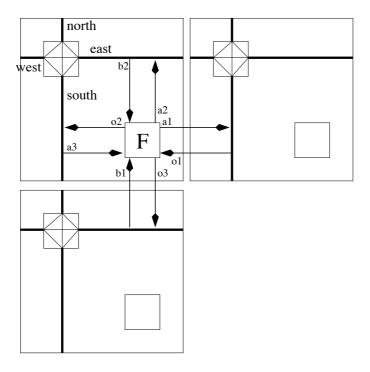

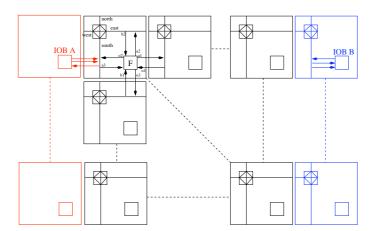

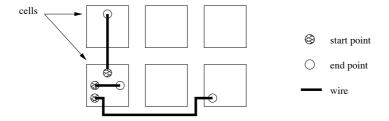

Within MADEO-bet, a reconfigurable architecture appears as a collection of 2-D grids of identical tiles. Each of these tiles can be either an atomic elements or a hierarchical composition of elements (figure 2.1).

The hierarchical elements contain either a 2-D grid of sub-elements owning their private position or a set of sub-elements that share the same location (e.g sub-elements within a CLB).

Atomic elements are functions, wires, switches, etc...

**Example** The architecture which serves as an example along this report is LPPGA developed by V. George [5]. The full model of this architecture is provided in appendix A. The FPGA appears as a 2D-grid of cells. These cells are composed of a logical function, a switch, some wires and some connections between these various elements (figure 2.2). However it's possible to define a more complex architecture for the elements of the table. For the LPPGA architecture there is only one level in the hierarchic architecture (figure 2.3).

#### 2.1.1 Method of design

The design of a FPGA with *Architecture Designer* is based on a grammar provided in the appendix B of this document or obtained while going in the menu  $Help \ \dot{e}$  BNF description. From this grammar it's possible to represent the architecture of the FPGA in a detailed way.

Once the architecture description is validated, Smalltalk classes are generated (paragraph 2.1.5) which represent every level of the hierarchy.

Despite these classes provide a sufficient support for the architecture, the developer has the opportunity to modify/optimize the produced code by hand in a classical Visualworks way (section 4.1.6).

Figure 2.1: Principles of design

#### 2.1.2 Hierarchical structure

#### 2D-Grids

A 2D-grid describes the regular replication of a given pattern. The information needed is the grid surface and its position on one hand, and the element to be replicated on the other hand.

```

(ARRAY (DOMAIN 1 1 x y) element )

```

Code Ex. 2.1: The ARRAY syntax

Note that heterogeneous architectures can be built by defining a set of domain-element couples. This is illustrated by the appendix A.3.

#### The composite elements

A composite element enables to group several objects within a single container in order to favor reuse/replication of elements. The composite elements do not only provide structural description but describe connections between elements as well.

In the example, the composite element corresponds to the FPGA cell. It recovers the list of elements as well as connections. The code representing the creation of a composite is as follows:

Figure 2.2: View of the functions IOs connections

```

(COMPOSITE

(

list_of_elements

)

list_of_connections

)

```

Code Ex. 2.2: The COMPOSITE syntax

<u>Note:</u> All the elements contained within a composite are accessible through their symbolic naming, so that all of them must be provided a name (2.1.4).

#### 2.1.3 The atomic elements

The set of available atomic elements is extensible under certain circumstances. This subsection does not detail the object-oriented rules the developer must conform to when creating a new kind of atomic element but introduces the most commonly used elements.

#### The functions

A function is a basic element which corresponds to the logical function of the cell. It is made up of a list of inputs and outputs and accepts potentially any "processing unit" assuming the IOs are compatible. However, the possible functions can be restricted to a set of symbols on demand.

Figure 2.3: Global view of the model. Note that the IOBs are encapsulated within composite elements in order to add lacking resources such as the right most vertical channel.

It is created in two ways, according to the kind of IOs enumeration (see codes 2.3, 2.4).

```

(FUNCTION

(INPUTS list_of_inputs)

(OUTPUTS list_of_outputs)

)

```

Code Ex. 2.3: The FUNCTION syntax with explicit naming

```

(FUNCTION

(INPUTS named input wire)

(OUTPUTS named output wire)

```

CODE Ex. 2.4: The FUNCTION syntax with global IOs

#### The wires

A wire is described by its width. A wire with a unary width is a single wire whereas a wire with a width above one can be either seen as a wire or as a channel owning tracks. This drives the behavior of the router as using single wire leads to global routing and using channels provides a detailed routing.

The wires do no set their range neither their population; these two characteristics are computed regarding the connections (see 2.1.4).

Figure 2.4: Example of action zone of wire

These two examples illustrate the use of a wire versus the use of a channel:

```

1. WIRE (WIRE (WIDTH size_of_wire))

2. SIMPLE CHANNEL (WIRE (WIDTH size_of_wire) EX-PANDED)

3. COMPLEX CHANNEL (WIRE (WIDTH size_of_wire) EXPANDED OF (wire *))

```

Code Ex. 2.5: The WIRE syntax

Note that there is no restriction on sub wires. Sub wires can be simple wires, channel or complex channels; they can be described as a link (see further on); they can be associated an individual representation.

#### The registers

```

(REGISTER

(INPUT string_describing_a_wire)

(OUTPUT string_describing_a_wire)

)

```

Code Ex. 2.6: The REGISTER syntax

#### The multiplexers

#### The switches

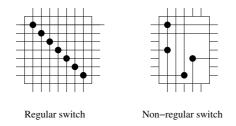

The switch permits to carry out the interconnection between two wires. It can carry out a regular interconnection or not (see fig. 2.5). In the case

```

(MULTIPLEXER

(INPUTS string_describing_a_wire * )

(OUTPUT string_describing_a_wire )

(WIDTH width)

```

Code Ex. 2.7: The MULTIPLEXER syntax

of the LPPGA the switch is regular. The definition of the switch is based on two parts, the first corresponds to the enumeration of the wires which are used by the switch, the second gives all connections carried out between different the wires used in switch. The creation of the switch is made using the code 2.8:

CODE Ex. 2.8: The SWITCHBLOCK syntax

Figure 2.5: Two examples of switches

In a matter of simplicity, a standard switch interconnecting wires of the same width is assumed to be a regular switch (see figure 2.5). In case widths differ and no particular connectivity is specified, the switch will be all-to-all connected. Note that this can bring surprising results when performing prospection (section 5) if the designer is not aware of linking the wires width.

#### The references

The references permit to call upon objects previously defined in another architecture to re-use them in new architectures. As every complex object is represented through a Smalltalk class, the name of the class acts as a parameter for reference. More information on classes definition is presented in the section **Category** (2.1.5).

(REFERENCE name\_of\_Class\_element )

Code Ex. 2.9: The REFERENCE syntax

#### 2.1.4 Accessing and connecting elements

#### Naming the elements

Naming the elements is required when aggregating elements within a composite. Note that the elements of the 2D-Grid are implicitly named by their position within the grid.

( unamed\_element NAMED name )

Code Ex. 2.10: Naming the elements

#### Accessing the elements

A hierarchical element accesses to its sub-elements using the *at:* syntax. The parameter is either a symbol or a point defining the position of the sub element.

As all elements know their container, relative addressing is also possible. Sending the *container* message to an element returns its container.

The example 2.11 addresses the element named f, contained in the same container that the requester.

myElement container at: #f

Code Ex. 2.11: Accessing the elements

#### Using aliases

For convenience some resources appear in several naming space (i.e. several composite elements). This is done using aliases which enable to delude the elements about the resource owning, without replicating shared resources. For example, shared lines often take advantage of owning several names.

```

( (LINK '(self relativeAt: position_of_target_cell) name_of_wire') NAMED name_of_second_wire )

```

Code Ex. 2.12: The LINK syntax

As the architecture appears as a regular pattern replication, some problems may happen on the borders. As an example, defining a tile made of a left and a up routing channel will produce degenerate right and bottom borders as some resources defined as links won't exist. A solution is to specify an exception to be raised on demand using an alternative syntax (code 2.13).

```

(LINK '(self relativeAt: position_of_target_cell) name_of_wire' IFNONE definition_of_the_alternative_element)

NAMED name_of_second_wire )

```

Code Ex. 2.13: The LINK alternative syntax

Another solution is to define an heterogeneous architecture (made of several domains), what allows to tune the borders to match the regularity requirements.

#### Connecting elements together

Connections are used to connect all elements of the cell. There are two types of connections: connections related to outputs and connections related to inputs.

```

(CONNECTION

'object_containing_output1 connect: output_name_1 to: wire'

'object_containing_output2 connect: output_name_2 to: wire'

...

)

```

Code Ex. 2.14: The CONNECTION syntax

```

(CONNECTION '(object_containing_input1 at input1) connectTa input2 of object_containing_ input2'  \dots \\ OR \\ '(object\_containing\_input1 \text{ at } input1) \text{ connectTa} \text{ } (object\_containing\_input2 \text{ at } input2)' \\ \dots \\ )

```

Code Ex. 2.15: The alternative CONNECTION syntax

For the second connections, two equivalent writings are available:

The connections are not limited to the current cell; it is possible to reach any cell of the circuit on demand through absolute/relative element addressing (see 2.1.4).

#### 2.1.5 Additional parameters

#### **Produce**

Marking out PRODUCE gives the possibility to create a Smalltalk class which name is passed as a parameter. Note that the name of class must to start with a **capital letter**.

```

(

( definition_of_element )

NAMED name_of_element )

PRODUCE Name_of_Class )

```

Code Ex. 2.16: The PRODUCE syntax

#### Category

Smalltalk classes are organized within categories. It's thus significant to group all the classes concerning the FPGA modeled in a single category. Marking out CATEGORY permits to direct the class generated by PRODUCE.

```

(

(

( definition_of_element )

NAMED name_of_element )

PRODUCE name_of_Class )

CATEGORY name_of_Category )

```

Code Ex. 2.17: The CATEGORY syntax

#### Representation

Simple graphical representations can be generated automatically based on some grammar informations. These informations are provided using the REPRESENTATION syntax element that takes place between the end of the definition of an object and the attribution of the name of this object.

CODE Ex. 2.18: The REPRESENTATION syntax

The options of REPRESENTATION are

- (COLOR *color*) to define the color of display of the object.

- (RECTANGLES x1 y1 x2 y2 ) to represent the object in form of a rectangle defined by the coordinates of the corner in top on the left (x1,y1) and the corner in bottom on the right (x2,y2).

- (CHANNEL x1 y1 x2 y2 vx vy) to represent the wires in the cell: (x1,y1) is starting point, (x2,y2) is ending point of the wire. The vector (vx, vy) represents spacing between the wires when option EXPANDED is used in the definition of the wire.

- (TEXT  $x \ y \ information\_to\_be\_displayed$ ) allows to display text starting from the position (x,y).

- $(name\_of\_wire \text{ (LINE } x1 \ y1 \ x2 \ y2 \ ))$  used by the switch this option gives space fixes to use to display the connected wires.

• (CUSTOM name\_of\_the\_custom\_method) enables to reuse custom representation whereas the generic representation is rebuilt.

#### Defining custom UIG for elements

The elements of the architectures are provided default UGI as shown in the 2.6 figure. Refining the *interfaceClass* parameter, associates a new hand made interface. The parameter must provide the name of the class describing the interface.

Figure 2.6: Some examples of the default user interface over the basic elements of he architecture

#### Defining customs parameters

The elements can be added some custom parameters to adapt to special needs. These parameters can be exploited by user-defined algorithms.

$({\rm SET}\ parameter\_name\ parameter\_value})$

Code Ex. 2.19: The custom parameters syntax

#### Defining variable parameters

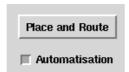

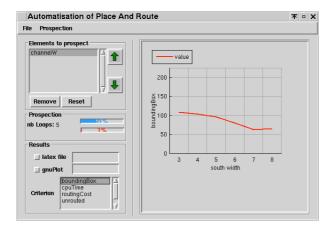

When prospecting the hardware definition space, the developer benefits from variable parameters allowing to perform loops in an automatic way. The produced results are collected. This is described in detail in section 5.

#### Setting the cost of the resources

It is possible to set the cost of every individual routing resource to influence the router's behavior. The default cost for a routing resource is 1. Adapting the cost of the resources depending on their range enables to favor the use of some resources (long lines, neighbor to neighbor connections, etc...).

This is done by setting the baseCost parameter.

( WIRE ( WIDTH size\_of\_wire (BASECOST number ))

Code Ex. 2.20: The BASECOST syntax

Note that using this parameter only enables to modify the router's behavior. To change the placer's behavior, changing the cost function is required (see appendix A.6).

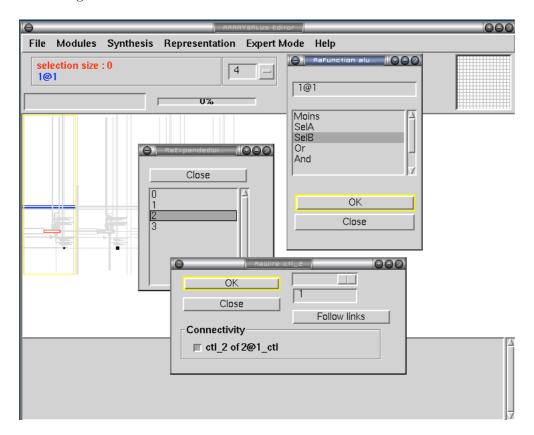

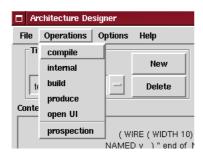

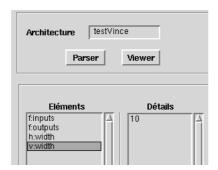

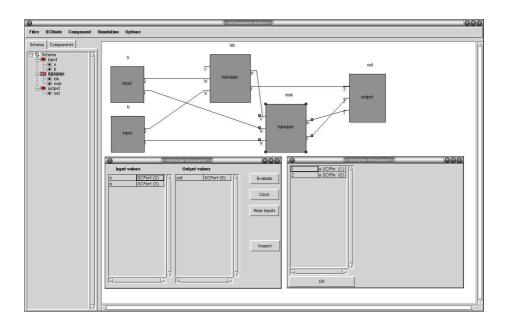

### 2.2 Using Architecture Designer

A convenient way to produce and use some architectural descriptions which are grammar compliant is to open the *Architecture Designer* tool. This tool facilitates common operations over textual descriptions such as compiling, saving/loading, producing the model, etc... and enables to invoke some other tools such as the user interface or the prospection automation tool.

#### 2.2.1 Loading/Saving an architecture

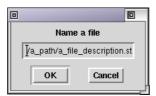

There are two methods to recover an architecture contained in a file using the menu of *Architecture Designer*.

The file list interface (see fig. 2.7) enables to select a file from which to load a piece of Smalltalk code. This is the standard Smalltalk way to load (file in) code within the environment. The code to be loaded describes an architecture through a set of classes that have been previously generated (section 2.2.3)

Figure 2.7: Loading an architecture description (1)

Figure 2.8: Loading an architecture description (2)

The user is asked to provide a path (a\_path) and the name of the file of a textual description to be loaded ( $a\_file\_description.st$ ). The files containing the description of an architecture have as an extension .st.

Saving your architecture is a menu operation in  $File \ \dot{c}$  save. At this point, a filename must be provided  $(a\_file.st)$ .

#### 2.2.2 Accessing/editing a description

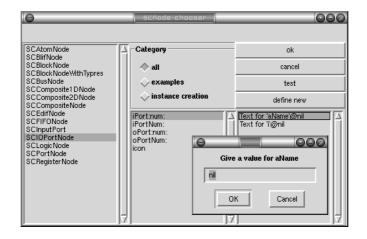

Selecting a description is done through a drop-down list in *Architecture Designer* (figure 2.9).

Figure 2.9: Selecting a description

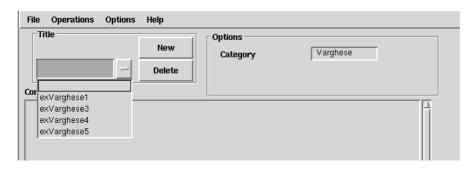

It's possible to restrict the search by indicating to which category belongs the architecture (figure 2.10). This requires to choose *Options* and to validate the check box *category*. An new input field enables to select the target category.

Figure 2.10: Choosing a category

#### 2.2.3 Starting with a new description

Creating a new architecture goes through clicking on the button New. The name of this new architecture must be provided in the input field on the left. The architecture is described in the text editor. However the architecture is not recorded in the drop-down list until the description is compiled. Compilation starts when clicking the compile button.

#### 2.2.4 Creating an architecture

The creation of an architecture defined in the text editor requires several stages. These stages are accessible through the buttons panel on the bottom of the window. Note that there is an inclusive relation between the operations from left to right (except the *open* button).

#### Compiling

The first stage, compilation, was already stated in a previous paragraph. It is represented by the button *compile* being on the interface, but can also be called by the menu *Operations*  $\dot{c}$  *compiles*. This stage checks if the description of architecture is grammar compliant (see appendix B).

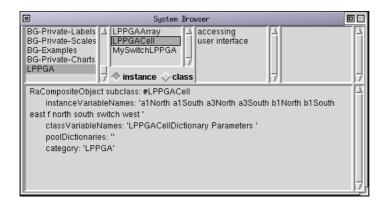

#### Generating Smalltalk classes

The creation of Smalltalk classes representing the architecture described in the text editor is done using the button build or with the menu Operations  $\dot{b}$  build. The name of the classes as well as the categories conform to the directive provided within the textual description. This is useful for advanced programming.

Figure 2.11: Code generated by build

The button *build* carries out compilation and classes' creation. Thus it's useless to click on *compile* before clicking on *build*. Options concerning the creation of the classes are available from the menu *Options*.

| Architecture | Description                                             |  |

|--------------|---------------------------------------------------------|--|

| LPPGACell    | Heterogeneous architecture                              |  |

| LPPGACell2   | LPPGA Simplified architecture, including ugi            |  |

| LPPGACell3   | LPPGA Architecture with regular function IOs            |  |

| LPPGACell4   | LPPGA Architecture with IOBs                            |  |

| LPPGACell5   | LPPGA Architecture with additional resources on borders |  |

Table 2.1: Provided examples

In case the option  $overwrite\ classes$  is set then each use of build generates all the classes to be crushed. In a similar way, the option  $overwrite\ representation$  crushes the Draw methods (graphical representation).

It's necessary to pay attention to the use of these two options. Any changes made in the automatically generated code will be lost if one of both option is selected. Preserving a hand written user interface remains possible using the CUSTOM parameter (2.1.5)

#### User interface over the FPGA

It is possible to visualize the FPGA starting from the button *open*, however the classes representing this FPGA must be already generated.

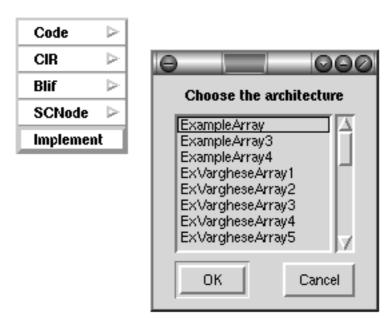

#### 2.2.5 Included examples

The code comes with a set of architectures definitions to enlighten the architectural grammar structure that have been presented in the previous section.

#### 2.2.6 Managing dependencies between elements

By defining complex elements, some dependencies are introduced. As an example defining a channel made of several sub channels may bring architecture building failure if the sub elements are provided a name within the channel's container name space. This situation happens very after as soon as multiples naming are used.

Another example is the IOs definition of multiplexers that commonly refers to external resources. Of course, this requires those resources to be created before the multiplexer attempts to link its IOs to the resources.

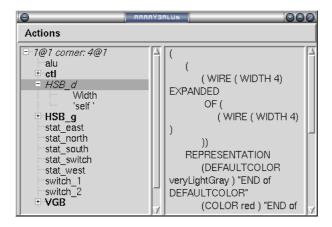

These cases require to order the elements, under the designer responsibility. The default ordering is based on ascending name sorting, nevertheless, using the TREE VIEW, this order can be adapted by elements drag and drop.

The figure 2.12 illustrates that mechanism. Getting up this tree view is got by clicking on the TREE VIEW button of the Architecture designer.

Figure 2.12: The tree representation of a composite

#### 2.3 Generating documentation

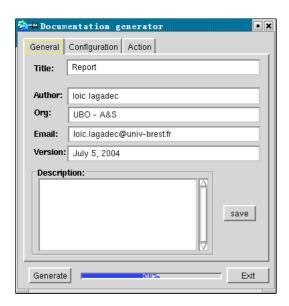

In order to ease the architecture definition versionning, a documentation generator is included within MADEO-Bet. This tool, called GenDoc, requires a Unix like OS to run properly.

#### 2.3.1 Principles

The main idea behind this is that writing documentation can be automated from the *UIArchitectureDesigner* tool. In fact, the documentation only provides a paper sheet with a tree view of the architecture, annotated by some icons to easily distinguish between the different kinds of elements, and by some comments the designer may add. The ?? appendix contains an example of report GenDoc can produce.

**Motivation** This automation is especially useful for joined works. Nevertheless, when letting an architecture description evolves, this allows to trace the evolution, as well as to set a version using the comment field (see figure 2.14).

**Pre-requires** The generator relies on LATEX. The report produces a LATEXfile, with graphical commands in it. Some encapsulated postscript figures are needed so that one of the parameters is the LATEX directory.

#### 2.3.2 Using MADEO-GENDOC

GenDoc is called from the ArchitectureDesigner tool by clicking on the right most button. This opens the 2.13 window. More complex parameter-

ization is possible by opening the 2.14 window. Note that default settings can be saved.

Actions The basic action is to generate the LATEX and the dvi files. A transcript window (figure 2.16) pops up after the job completes.

Getting some additional formats requires to select the adequate options. Several formats can be chosen as output: postscript, pdf, html. The pdf file is produced by the ps2pdf command, the html is made by calling latex2html. the html description (figure 2.17) includes hyper links that ease the navigation through the architecture elements.

The other actions are viewing the postscript, generating the pdf, viewing the pdf.

Figure 2.13: The GenDoc user interface

## 2.4 VHDL generation

MADEO-bet allows to bring up a set of tools to program any architecture before any hardware realization. This ensure good properties such as early architecture evaluation, that lets SOC use of reconfigurable make sense. Regarding the classical design flow starting with writing a VHDL description of the architecture before synthesizing it and finally re-writing tools to tune them in order to apply on the new architecture, Made-bet offers an alternative flow making the tools a starting point.

Nevertheless, after the designer has defined its target hardware, as an example by taking advantage of the hardware prospection capabilities of MADEO-BET, the VHDL writing step still remain to be done.

Figure 2.14: The GenDoc parameters

Figure 2.15: The GenDoc actions

Figure 2.16: The GenDoc transcript

Figure 2.17: The GenDoc html output

#### 2.4.1 Principles

To shortcut this step within the design flow a current work aims to provide automatic VHDL code production based on the grammar describing the hardware.

**Motivation** The goal is not to compete with "general purpose FPGAs" vendors such as Xilinx but rather to get an output enabling physical synthesis of custom dedicated FPGAs in a SOC scope.

This offer an after synthesis accurate feed-back to tune the algorithm parameters in one hand, and suppress the manual intervention of the designer in the other hand.

**Pre-requires** A VHDL model has been developed that encapsulates not only the syntax of VHDL but also supports the hierarchical approach, and modular decomposition of the code.

The set of classes is made of three types of objects:

- the classes that match the basic constructs of the language (entity, if then else, port, etc...),

- the classes that offer a support for recurrent constructs (luts, switches, etc...),

- some classes that handle internal constructs (parenthesis, indexes, etc...).

All the classes own a modular generation of textual representation, and are provided with examples<sup>1</sup>.

The key issue is to validate an right instantiation of this model from the MADEO-BET model. As the MADEO-BET model is made of atomic objects and compositions mechanisms, the VHDL model supports atomic constructs and complex combinations of objects through a mechanism of port mapping.

#### 2.4.2 Using VHDL Producer

This interface is not working at this time.

<sup>&</sup>lt;sup>1</sup>as class methods

## Chapter 3

# Programming an architecture

#### 3.1 Introduction

This section describes what 'programming a reconfigurable architecture' means. As well, it highlights the difficulty to route FPGAs, as compared to ASICs.

#### 3.2 Towards new needs

This section describes the new needs in term of flexibility (to different families as well as to defaulted instances of an architecture), short development time and algorithmic quality (modularity / reuse), support for upper layers and inter-operability.

This section argues as well that the tools must be used as early as possible in the design process of a new architecture, as it's the only way to get an accurate feed back after tuning finely the architecture description; and that tools must be decoupled from the target architecture.

#### 3.2.1 Algorithms

This section introduces some well known algorithms and select some of them that have been picked up to be implemented within MADEO.

## Chapter 4

## Tools

### 4.1 Using FPGA Editor

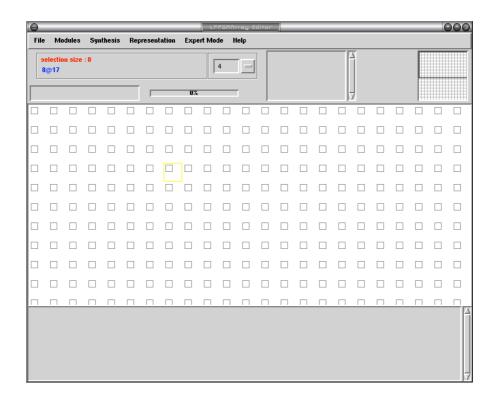

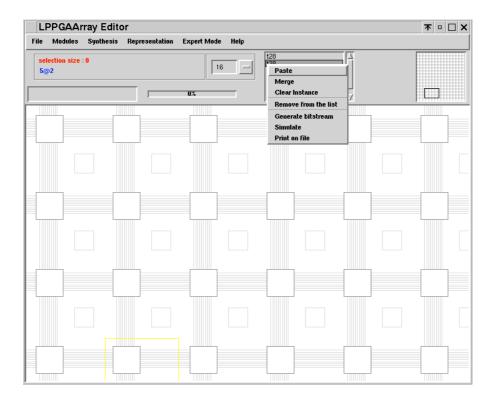

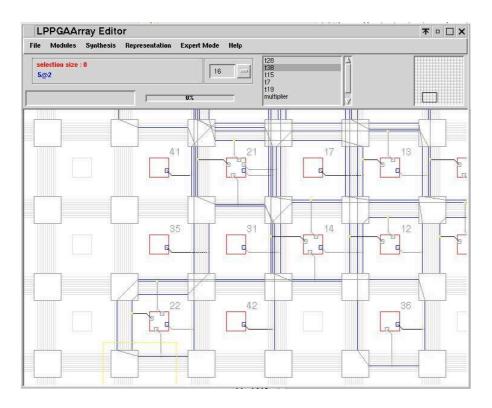

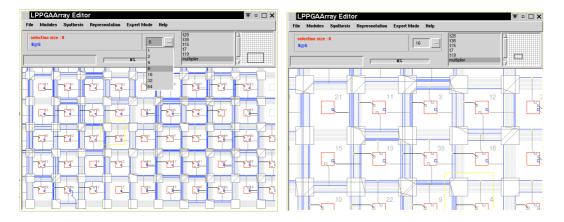

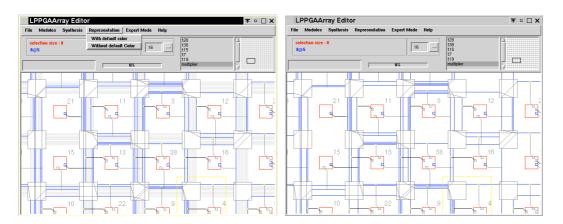

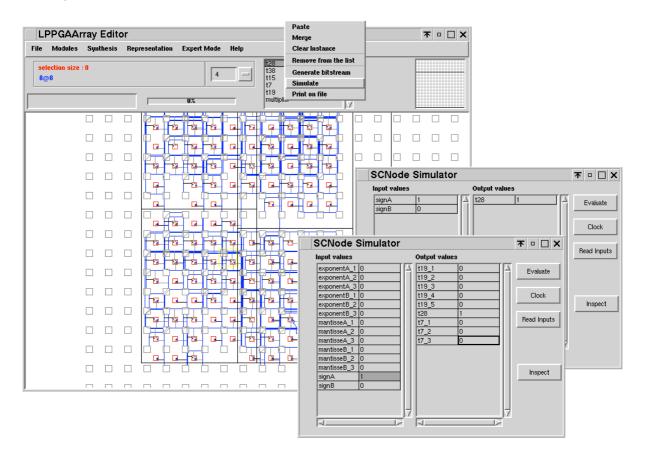

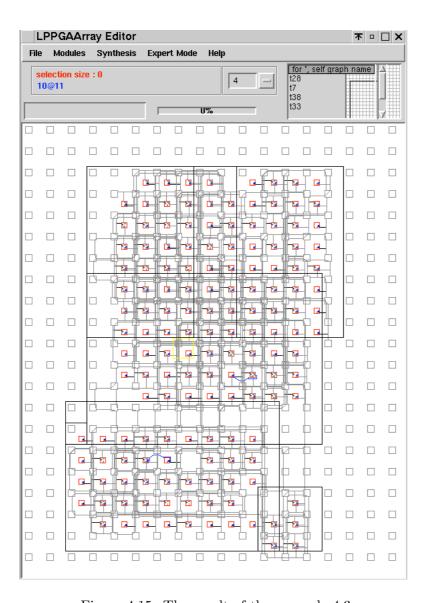

$FPGA\ Editor$  (see fig. 4.1) is a tool which makes it possible to visualize and to handle an architecture created with  $Architecture\ Designer$ .

The interface is made of three parts: the first one corresponds to the menu, the second one is a view of the FPGA and the third one is command line zone.

Figure 4.1: The interface of FPGA Editor

#### 4.1.1 Application description

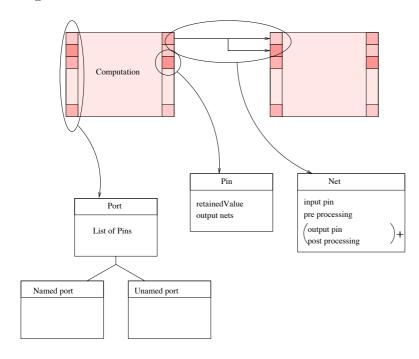

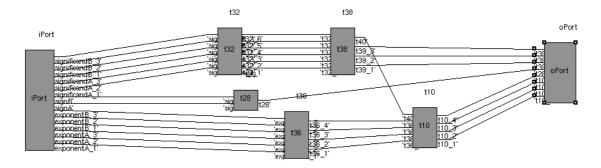

This describes the several levels of application description. The application is described over a set of objects which support the same API but own different levels of abstraction. All these objects are SCNodes; they encapsulate a computational description and own IO ports which handle dependencies in order to support change propagation over the values they retain.

The connectivity between nodes is relevant to the IO ports' pins.

What differentiates between the types of nodes is the kind of computational description the carry: BLIF, EDIF, Smalltalk block, etc.... As well there are some hierarchical constructs, as illustrated by the 4.5 example.

The figure 4.2 illustrates this formalism.

Figure 4.2: The application description formalism

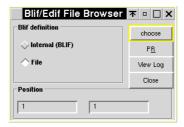

#### 4.1.2 Selecting BLIF/EDIF files

The Modules ¿ BLIF ¿ Place and Route has BLIF description menu (see fig. 4.3) enables to choose a file to be placed/routed on the architecture.

The appearing window lets the designer free to choose the file to place and route, to regulate the orientation of the routing and to give a position to start place and route.

Figure 4.3: Selecting a BLIF/EDIF file from the menu

Figure 4.4: BLIF/EDIF File Browser

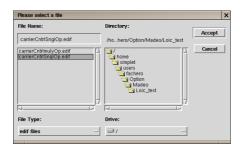

To select a file the user either types the name of the file with the complete path in the input field, or clicks on the button *choose*. Clicking on *choose* makes a *file list* to open (fig. 4.5).

Figure 4.5: selecting a BLIF/EDIF file

#### 4.1.3 Placing and routing a BLIF/EDIF file

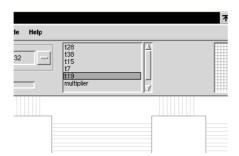

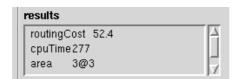

Once parameterized the *BLIF file browser*, clicking on the button  $P \mathcal{C}R$  places and routes the modules. The name of the new module appears in the drop-down list of the menu (fig 4.6).

Figure 4.6: The list of available modules

Note that the EDIF format supports location constraints for the functions. Theses constraints are added using the FPOS property field. the location are relative to the bottom left corner of the module.

#### 4.1.4 Pasting the module

The selected cell acts as the bottom left anchor when pasting a module. This cell is yellow bordered and is selected using the mouse. Pasting the module is done by choosing the correct option in the menu associated with the list of modules (figure 4.7). The figure 4.8 shows the result of pasting a module. Note that this action does not trigger a new place and route process but relies on a previous place and route, that produced the module.

Figure 4.7: Pasting the module on the FPGA

If the display is too small, the enlarging of the FPGA can be changed by choosing a factor in the small drop-down list. This is illustrated through the figure 4.9.

Another representation option (depending on the grammar definition of the architecture) allows to draw either all the resources, which is useful to estimate the routing congestion, or only the used resources, which makes the drawing simpler. The figure 4.10 illustrates how to swap between the two modes. 54 CHAPTER 4. TOOLS

Figure 4.8: After pasting the module on the FPGA

Figure 4.9: Selecting the zoom factor

Figure 4.10: Representing either all or only used resources

#### 4.1.5 Simulating the circuit

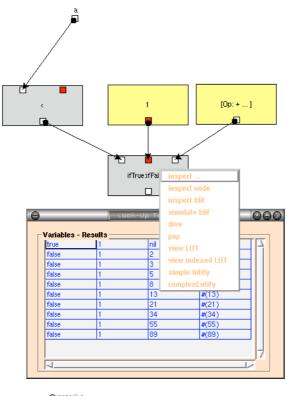

Once placed and routed, a circuit can be simulated as illustrated in the figure 4.11 by using the *simulate* option of the module's menu. The simulation process does not rely on the P&R information but limits itself to analyzing the netlist. Both simple and hierarchical descriptions can be simulated.

As an example the figure 4.11 shows a hierarchical circuit which submodules' bounding boxes are drawn, and on the right the result of simulation. Either the global circuit (front window) and a one of its submodules (back window) are simulated.

Figure 4.11: The simulation of P&R circuits

#### 4.1.6 Using the window commands

The command line area of the window enables complex manipulations over the architecture, such as in depth inspection of the resources and debugging.

here is a list of simple examples of useful commands to recover information on the FPGA follow:

#### self model

Inspecting this code (button medium of the mouse and *inspect*) returns the Smalltalk object representing FPGA circuit.

#### self model modules values

Inspecting this code returns the list of circuits implemented within the FPGA (each of which owns several instances).

#### (self model modules values at: i) benchmark

Inspecting this code returns the place&route benchmark of the  $i^{th}$  module.

(((self model modules values at: i ) instances) at: #instance1) elements

Inspecting this code returns the placement information of the instance #instance1 of the  $i^{th}$  module

(((self model modules values at: i ) instances) at: #instance1) routes asOrderedCollection

Inspecting this code returns the routing information of the instance #instance1 of the  $i^{th}$  module

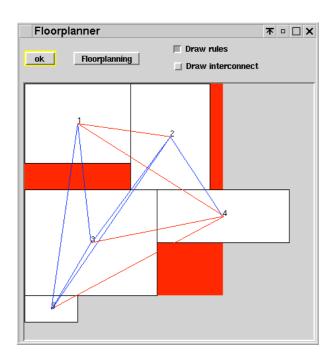

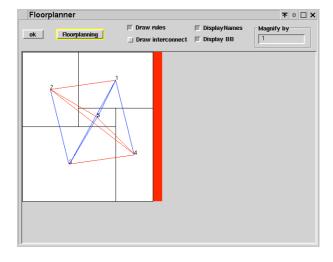

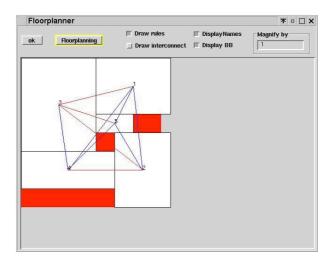

### 4.2 Floor planning

The floor planning is based on [12]. A floorplan is described as an assembly of rectangles and a set of constraints regarding the relative locations of the rectangles. Four basis operation apply on the floorplan:

rotate transposes the extent of the rectangular bounding box of a module

swap exchanges two modules

**reverse** reverses the relation between two modules (eg.  $i \perp j \longmapsto j \perp i$  where  $\perp$  is either left or above and i,j are two modules)

**move** modifies the type of relation (eg.  $left \mapsto above$ )

The floorplanner performs an annealing schedule over the floorplan, using these four operations. The cost function takes into account the global bounding box of the assembly, the part of this bounding box which does not match the constraint bounding box requirements and the interconnection cost (see code 4.1).