# Automated Generation of Heterogeneous Multiprocessor Architectures: Software and Hardware Aspects

Youenn Corre

# ▶ To cite this version:

Youenn Corre. Automated Generation of Heterogeneous Multiprocessor Architectures: Software and Hardware Aspects. Hardware Architecture [cs.AR]. Université de Bretagne Sud, 2013. English. <tel-01130482>

# HAL Id: tel-01130482

https://hal.archives-ouvertes.fr/tel-01130482

Submitted on 11 Mar 2015

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE / UNIVERSITÉ DE BRETAGNE SUD

sous le sceau de l'Université Européenne de Bretagne

Pour obtenir le grade de : DOCTEUR DE L'UNIVERSITÉ DE BRETAGNE SUD Mention : STIC École Doctorale SICMA présentée par

# Youenn Corre

Laboratoire des Sciences et Techniques de l'Information, de la Communication et de la Connaissance

# **Automated Generation of Heterogeneous Multiprocessor Architectures: Software and Hardware Aspects**

Thèse soutenue le 23 janvier 2013,

devant la commission d'examen composée de :

Pr. Smail Niar

Professeur, LAMIH - Université de Valenciennes / Président

Pr. Daniel Ménard

Professeur, INSA Rennes / Rapporteur

**Pr. Frédéric Rousseau** Professeur, TIMA - UJF Grenoble / Rapporteur

Dr. Dominique Heller

Ingénieur de Recherche, Lab-STICC - UBS Lorient / Encadrant de thèse

Pr. Loïc Lagadec

Professeur, Lab-STICC - ENSTA Bretagne / Co-directeur de thèse

Dr. Jean-Philippe Diguet

Directeur de Recherche CNRS, Lab-STICC - UBS Lorient / Directeur de thèse

# Résumé

Les systèmes embarqués sont aujourd'hui omniprésents et les progrès d'intégration accompagnant cette évolution permettent d'accroître leurs fonctionnalités et capacités potentielles. Cette coévolution a conduit à l'emergence des systèmes-sur-puce multiprocesseurs hétérogènes qui répondent aux contraintes des systèmes embarqués en termes de performances et d'énergie. Cependant cet avantage se traduit par une complexité de conception et de programmation accrue. Le niveau d'expertise requis ainsi que le temps de développement limitent considérablement leur déploiement, il est donc nécessaire de réaliser des outils permettant d'affranchir les concepteurs des détails architecturaux et de programmation afin qu'ils puissent mobiliser leurs efforts sur les étapes à forte valeur ajoutée. L'objectif est donc d'automatiser les tâches fastidieuses et chronophages propres à la conception d'architectures multiprocesseurs hétérogènes, notamment sur FPGA, en élevant le niveau d'abstraction selon une approche qui unifie la synthèse de haut-niveau et la co-conception logicielle/matérielle au-delà des approches existantes qui se révèlent partielles ou inadaptées.

Les travaux de cette thèse sont une réponse à ce problème, ils présentent un outil de conception reposant sur le principe d'une automatisation des tâches fastidieuses et laissant la main au concepteur là où celui-ci le souhaite. Pour cela, on s'appuie sur un modèle d'architecture défini à l'aide d'un formalisme de haut-niveau indépendant des détails d'implémentation, palliant ainsi l'absence d'architecture multiprocesseur sous-jacente dans les FPGA. Ce modèle de spécification permet également au concepteur de fournir les contraintes à différents niveaux de détails en fonction de ses connaissances du système ou de son niveau d'implication. L'exploration de l'espace de conception se fait grâce à un algorithme scalable et reposant sur des estimations rapides et précises. Une méthode d'exploration des accélérateurs matériels, utilisant la synthèse de haut-niveau pour une estimation rapide des coûts, est introduite. Enfin, l'intégration de méthodes d'ingénierie dirigée par les modèles permet la génération du design final et notamment des fichiers d'implémentation en fonction de la cible, facilitant ainsi la portabilité et la réutilisation des designs. L'outil a été validé à travers deux études de cas: un décodeur vidéo MJPEG et une application complexe de détection de visage.

**Mots-clés**: Systèmes-sur-puce multiprocesseurs hétérogènes, FPGA, Conception électronique assistée par ordinateur.

### **Abstract**

Embedded systems are now ubiquitous and the increase in the integration capacity allows for more features and capabilities. This trend has led to the emergence of Heterogeneous Multiprocessors Systems-on-Chip (H-MPSoC) which provide a way to respect the cost and performance constraints inherent to embedded systems. However they also make the task of designing and programming such systems a long and arduous process. The skills required along with the long development time are obstacles to their diffusion. It is thus necessary to develop tools that will free designers from architectural and programming details, so that they can focus on the tasks where they can bring added-value. The objective is thus to automatize the tedious tasks that burden the design of H-MPSoC, in particular on FPGA, by providing a higher-level of abstraction following a method that brings together High-Level Synthesis and hardware/software codesign beyond the existing solutions which are whether incomplete or unfit.

The presented work aims at providing an answer to these problems. They introduce a design framework relying on the automation of tedious tasks and allowing designers to express their expertise where they want to. For this, we rely on an architecture model defined with a high-level formalism independent from implementation details, providing a solution to the lack of multiprocessor architecture in FPGAs. This specification model also allows designers to provide design constraints in accordance with their level of expertise or involvement. The design space exploration is implemented as a scalable algorithm relying on fast and accurate estimation techniques. A method for the exploration of hardware accelerators based on high-level synthesis to provide fast cost estimations is introduced. Finally the integration of model-driven engineering methods enables portability and reuse by generating the final design implementation. The framework is validated through two case studies: an MJPEG video decoder and a more complex face detection application.

**Keywords**: Heterogeneous Multiprocessors Systems-on-Chip, FPGA, Electronic-System Level Design.

n° d'ordre:

Université de Bretagne-Sud

# Atchoum!

Victor Hugo, un jour de grand froid.

# Remerciements

Je remercie mon Directeur de thèse, Jean-Philippe Diguet, pour son encadrement, sa grande disponibilité, ses nombreuses idées et ses conseils tout au long de la thèse. Merci à Loïc Lagadec, qui a été mon encadrant principal durant la première année, pour ses remarques parfois difficiles à entendre mais toujours justes et pertinentes. Je remercie Dominique Heller pour son aide et son expertise qui m'ont été très utiles durant ces trois ans. Merci également à Koen Bertels de m'avoir accueilli pour trois mois au sein de son équipe à TU Delft.

Je remercie M. Smail Niar d'avoir accepter de présider mon jury de thèse. Je remercie également MM. Daniel Ménard et Frédéric Rousseau d'avoir réaliser les rapports du présent mémoire malgré le peu de temps dont ils disposaient.

Je remercie les nombreuses personnes que j'ai eu l'opportunité de croiser au cours de ces trois ans : l'équipe Architectures & Systèmes de Brest, l'équipe de Computer Engineering à l'Université technologique de Delft et les membres du Lab-STICC Lorient pour l'ambiance unique qui y règne. Merci également aux nombreux doctorants que j'ai rencontrés, trop nombreux pour être tous cités ici, et avec qui j'ai passé de bons moments.

Enfin, je remercie mes amis et ma famille, mon père, ma mère et Brenda, ma grande sœur, pour leur soutien tout au long de cette thèse.

# Contents

| Co | onter | its      |                                                            | L |

|----|-------|----------|------------------------------------------------------------|---|

| 1  | Intr  | oducti   | ion .                                                      | 5 |

|    | 1.1   | Contri   | ibutions                                                   | 7 |

|    | 1.2   | Outlin   | ue                                                         | 3 |

| า  | C+-   | te of tl | ne Art                                                     | ` |

| 2  |       |          |                                                            |   |

|    | 2.1   |          |                                                            | 9 |

|    | 2.2   |          | ng MPSoC Design Tools                                      |   |

|    |       | 2.2.1    | Daedalus                                                   |   |

|    |       | 2.2.2    | SystemCoDesigner                                           |   |

|    |       | 2.2.3    | Advanced Systembuilder                                     |   |

|    |       | 2.2.4    | hArtes                                                     |   |

|    |       | 2.2.5    | PeaCE                                                      |   |

|    |       | 2.2.6    | Xilinx XPS                                                 |   |

|    |       | 2.2.7    | Space CoDesign                                             | 3 |

|    |       | 2.2.8    | Conclusion                                                 | ) |

|    | 2.3   | High-I   | Level Synthesis Tools                                      | 3 |

|    |       | 2.3.1    | Gaut                                                       | 3 |

|    |       | 2.3.2    | LegUp                                                      | 1 |

|    |       | 2.3.3    | C2H                                                        | 1 |

|    |       | 2.3.4    | CyberWorkBench (CWB)                                       | 5 |

|    |       | 2.3.5    | Bambu                                                      | 5 |

|    |       | 2.3.6    | AutoESL's AutoPilot                                        | 3 |

|    |       | 2.3.7    | Conclusion                                                 | 3 |

|    | 2.4   | MDE-     | based Design of MPSoC                                      | 3 |

|    |       | 2.4.1    | Model Driven Engineering for MPSoC DSE                     |   |

|    |       | 2.4.2    | Multilevel MPSoC Simulation using an MDE Approach 2        |   |

|    |       | 2.4.3    | A Co-design Approach for Embedded System Modeling and Code | , |

|    |       | 2.1.0    | Generation with UML and MARTE                              | Q |

|    |       | 2.4.4    | Conclusion                                                 |   |

|    |       | 2.1.1    | Conclusion                                                 | , |

| 3  | Flo   | w of th  | ne Framework 29                                            | ) |

|    | 3.1   |          | Global Overview                                            |   |

|    |       | 3.1.1    | Tool Implementation                                        |   |

|    |       | 3.1.2    | Target Architecture                                        | ) |

|    |       | 3.1.3    | Inputs                                                     | 1 |

|    |       | 3.1.4    | Flow Overview                                              | ó |

|    |       | 3.1.5    | Automated Profiling                                        | 7 |

|    | 3.2   | Extern   | nal Tools                                                  | 3 |

|    |       | 3.2.1    | HLS Tool                                                   | 9 |

|    |       | 3 2 2    | Daedalus 30                                                | a |

# Contents

|   |     | 3.2.3 Xilinx XPS                                      | 2 |

|---|-----|-------------------------------------------------------|---|

|   | 3.3 | Database-based Strategy                               | 2 |

|   |     | 3.3.1 Template Architecture Database                  | 2 |

|   |     | 3.3.2 Hardware Accelerators Database                  | 3 |

|   |     | 3.3.3 FPGA Model Database                             | 4 |

|   |     | 3.3.4 Reuse-based Strategy                            | 4 |

|   | 3.4 | Conclusion                                            | 4 |

| 4 | Des | ign Space Exploration Methodology 45                  | 5 |

|   | 4.1 | DSE Algorithm                                         | 5 |

|   |     | 4.1.1 Algorithm                                       | 7 |

|   |     | 4.1.2 Explanations                                    | 9 |

|   | 4.2 | Performance & Cost Estimation                         | 1 |

|   | 4.3 | Hardware Accelerators Exploration                     | 2 |

|   |     | 4.3.1 HLS-based Estimations                           |   |

|   |     | 4.3.2 Pareto-optimal Selection                        |   |

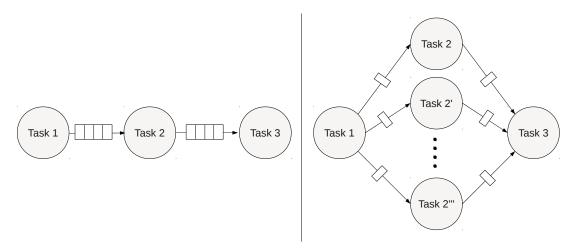

|   | 4.4 | Data Parallelism Exploration through Task Duplication |   |

|   | 4.5 | Communication & Memory Model                          |   |

|   |     | 4.5.1 Congestion Detection                            |   |

|   | 4.6 | Data-Task Mapping & Scheduling Strategy               |   |

|   |     | 4.6.1 Data Mapping                                    |   |

|   |     | 4.6.2 Task Mapping                                    |   |

|   |     | 4.6.3 Scheduling                                      |   |

|   | 4.7 | Conclusion                                            |   |

| 5 | Ten | aplate-based Approach 71                              | 1 |

| • | 5.1 | Introduction to MDE                                   |   |

|   | 5.2 | Application to FPGA-based Design                      |   |

|   | 5.3 | AADL                                                  |   |

|   | 0.0 | 5.3.1 Eclipse Modeling Framework                      |   |

|   | 5.4 | Component Models                                      |   |

|   | 5.5 | Specification Template                                |   |

|   | 0.0 | 5.5.1 Template Configuration Interface                |   |

|   | 5.6 | Code Generation                                       |   |

|   | 0.0 | 5.6.1 Software Application Adaptation                 |   |

|   |     | 5.6.2 Implementation Project Files                    |   |

|   | 5.7 | Conclusion                                            |   |

|   |     |                                                       | _ |

| 6 | Res |                                                       |   |

|   | 6.1 | Application 1: MJPEG decoder                          |   |

|   |     | 6.1.1 Presentation                                    |   |

|   |     | 6.1.2 Specifications                                  |   |

|   | 0.0 | 6.1.3 Results                                         |   |

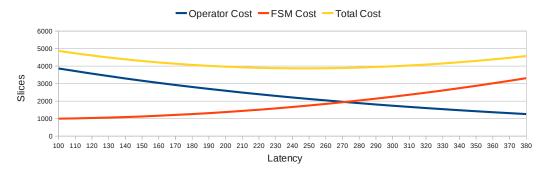

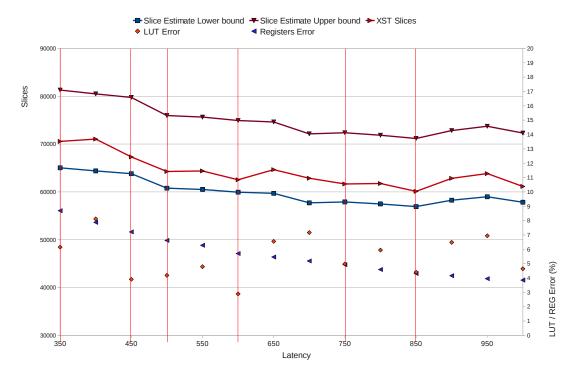

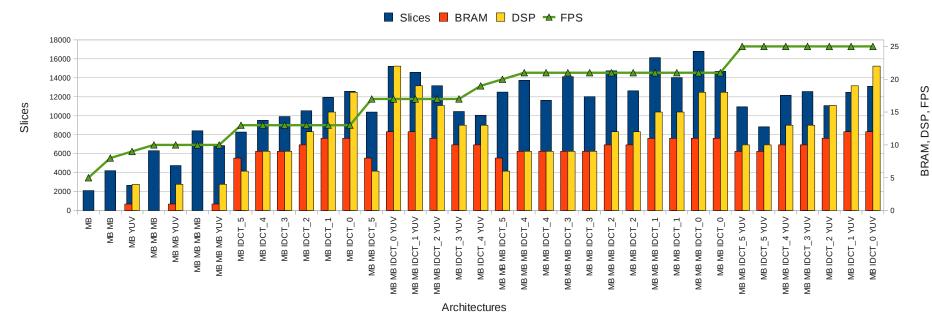

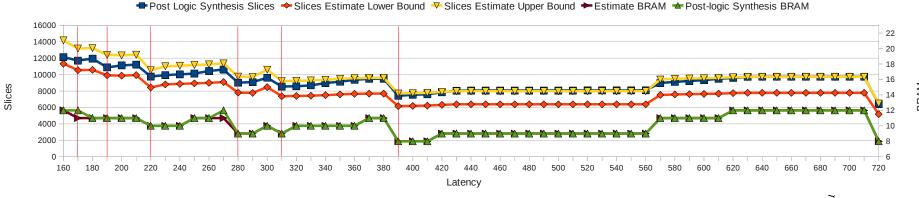

|   | 62  | Hardware Accelerators Exploration 9                   | 1 |

|                  |            |                         |                     | C | Con | tents                      |

|------------------|------------|-------------------------|---------------------|---|-----|----------------------------|

|                  | 6.3        | 6.3.1<br>6.3.2<br>6.3.3 | IDCT IP Exploration |   |     | 94<br>94<br>95<br>96<br>97 |

| 7                |            | clusion                 |                     |   |     | 111                        |

|                  | 7.1<br>7.2 |                         | ary                 |   |     |                            |

| 8                | Bib        | liograp                 | ohy                 |   |     | 115                        |

| Li               | st of      | Public                  | cations             |   |     | 119                        |

| Li               | st of      | Figure                  | es                  |   |     | 121                        |

| Li               | st of      | Tables                  | 3                   |   |     | 123                        |

| Li               | st of      | Algori                  | ithms               |   |     | 125                        |

| $\mathbf{G}^{1}$ | lossaı     | ry                      |                     |   |     | 127                        |

# Contents

# Introduction

Embedded systems are now more than ever part of daily life. This ubiquity also means diversity, as embedded systems can take many forms, from a portable camera to system control in airplanes and include smartphones, set top boxes, cameras, GPS, etc. All these apparels tend to grow in features and consequently their designs also grow in complexity.

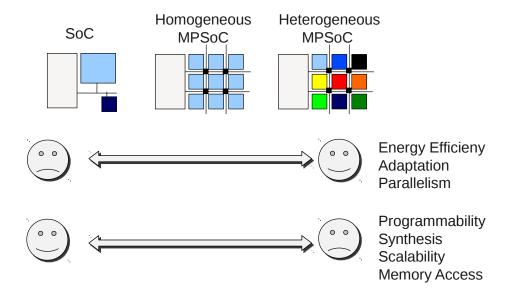

In order to be able to deal with the typical constraints of embedded systems — performance, size and power consumption — in spite of the increasing complexity, a new type of system was developed: System-on-Chip (SoC). SoCs gather on one single chip all the necessary components for a complete system, i.e. processing units, memories, communication buses, peripheral controllers, Analog/Digital converters and so on. SoCs are thus an efficient way to provide the required performances while reducing the size and the power consumption of the system. Designing SoCs however is a complex task that requires skill and knowledge in order to balance performances, size and power consumption. When designing such systems, lots of decisions have to be taken due to the large number of design options, leading to larger design space. Due to the increasing complexity of SoCs, such decisions can no longer be taken manually without being a highly error-prone process and cannot be performed within a reasonable time.

Heterogeneity SoCs have then evolved toward multiprocessor architectures, to answer the growing demand for computation power, leading to homogeneous Multiprocessor Systems-on-Chip. This introduced parallel programming at the software level in the design flow, along with the problems inherent to this programming paradigm, i.e. mapping, communication and synchronization. Then MPSoCs evolved toward Heterogeneous Multiprocessor Systems-on-Chip, which include specialized processing units, in order to answer the necessity to have better system performance and energy-efficiency. This has also brought new design difficulties: partitioning and design of hardware accelerators. These new design steps were out of scope of software engineers and thus required new skills. This thus lead to the necessity for companies to adapt by hiring hardware engineers, thus leading to increased development costs making development of such systems riskier, especially for Small and Medium Enterprises (SME).

Off-the-shelf H-MPSoCs are available, for instance the Texas Instruments OMAP processors [1] are a family of H-MPSoC present in many smartphones. However these

### Introduction

H-MPSoCs have fixed architectures and are usually designed for widespread application domains. Consequently, they cannot be easily adapted to specific domain and can thus be oversized in regards to the system requirements. Moreover, the specialized processing units cannot be easily programmed.

H-MPSoC is a domain where innovation is still active. In 2012, Xilinx has released the Zynq Field-Programmable Gate Array (FPGA) board [2], which associates a multiprocessor SoC with FPGA capabilities, bringing reconfigurability into SoCs. The advantage means that it is possible to adapt the hardware accelerators accordingly with the current needs of the system. Another advantage is the possibility to adapt the system to evolution, which is useful especially in long-life system such as military applications, satellites, cyber-physical systems, etc.

**FPGA Design Complexity** The development of systems such as SoCs usually goes through a prototype phase, prototype which is typically implemented on a FPGA for validation. However designing for FPGA is still a costly process, despite the design tools provided by FPGA manufacturers. In [3], a comparison is made in the development of a high-performance application on different targets: an x86-based General Purpose Processor (GPP), a Graphical Processing Unit (GPU) and an FPGA. The study clearly shows the advantages of FPGA in terms of energy-efficiency and performances over the other solutions. For the studied application, the speedup over GPP is of two orders of magnitude with an energy consumption three orders of magnitude lower than the GPP. However the study also shows that it remains a very long and very costly process, most of the cost coming from the long development time. The development time is two orders of magnitude greater than the one for GPP with a cost one order of magnitude greater. The authors of the study suggest that the reasons of these flaws in FPGA design are due to the difficulty to master FPGA design and debug processes. They also point out the lack of standards which prevents all backward and onward compatibility, thus prohibiting design portability and reuse.

Moreover FPGA design is a very time-consuming process due to the different stages of the implementation: synthesis, mapping, place and route and test. This fact supports the point of view in the industry that FPGA is a risky product, which has low productivity and is consequently associated with longer time-to-market. Hence the necessity to have a way to reduce the implementation time by providing accurate pre-implementation evaluations of a design both in size and performance and to provide validated and thus bug-free systems in order to minimize the debug phase.

**Design Tools Tediousness** Along with chip capabilities, tools complexity has increased from time to time and another difficulty encountered by designers is thus the tediousness of the design tools that contain numerous configuration options which can be confusing and can easily lead to make mistakes consequently very hard to debug. For these reasons, it is necessary to find tools to simplify the design process of such systems and thus increase the designer productivity. This can be done by automating the tedious parts of the design process in which designers cannot bring any added-value.

In embedded systems, the frontier between hardware and software domains is fuzzy and consequently the design of one is dependent of the other. This is problematic since typical software engineers and hardware engineers have design approaches that differ greatly and they are usually not aware on how things are done in the other domain. There are few engineers who master how both worlds work and thus it is a rare and valuable skill. That problem can be overcome by providing on the one hand a high-level of abstraction in which the distinction between hardware and software is not made, and on the other hand by automating the design decisions and in particular the partitioning between hardware and software implementations.

# 1.1 Contributions

All these reasons show that the design of H-MPSoC for FPGA is a tedious, error-prone and costly process, leading to the necessity to have a tool to assist designers in order to simplify and speedup the design process. In this thesis, we present a framework for the automation of the design of efficient H-MPSoC. Given an application, a basic architecture template and a set of constraints, the framework explores the design space and generates a complete system including the synthesizable hardware platform and the adapted C code respecting the provided constraints. To achieve this goal, several dimensions are explored: the number and type of processors, the hardware specialization, the data parallelism exploitation, the communication and memory models, mappings and schedulings. However designers have the control of the flow and can introduce design decisions according to their design skills.

The contributions of this thesis are:

- A framework that automates the tedious phases of the H-MPSoC design in order to let designers focus where their knowledge is most needed. Our framework also generates a correct-by-design code for both the hardware and software implementations. This avoids the error-prone design process provided by current FPGA design tools, and since it lowers the cost of the design process to the implementation, more designs can be further explored.

- An automated and scalable Design Space Exploration (DSE) algorithm that takes into account size and performance constraints and relies on fast and accurate estimators. This simplifies the design by exploring the numerous design options of H-MPSoCs and by evaluating them in order to propose a set of Pareto-optimal options to the designer. Explored dimensions include hardware accelerator choice, processor allocation, task mapping, memory selection and data mapping. The scalability factor also allows the designer to balance between the time spent for optimizing the results, consequently optimizing the designer productivity.

- The integration of a fast and automated exploration of hardware accelerators in the DSE loop by means of High-Level Synthesis (HLS). This offers more design options by providing a tradeoff between cost and performances and allows to fully exploit the heterogeneity of H-MPSoC.

### Introduction

- The integration in the DSE loop of the data parallelism exploration through task duplication in order to further speedup the designed system.

- The use of Model-Driven Engineering (MDE) methods through the integration of a template-based approach to describe the input architecture. This template let designers configure the exploration according to their own level of expertise, while also abstracting away target-specific implementation details. This also favors design portability and reuse by providing a solution to the absence of FPGA standards.

- A strategy favoring reuse through the use of databases in order to speedup the design process.

# 1.2 Outline

This manuscript is structured as follows:

- Chapter 2 describes the state of the art in ESL design tools for MPSoC, in HLS tools, and in the usage of MDE for DSE of MPSoC.

- Chapter 3 presents an overview of the framework flow.

- Chapter 4 introduces our DSE algorithm: the explorations methods are detailed along with the used estimation techniques for cost and performance evaluation.

- Chapter 5 explains how we use MDE methods to simplify, to favor reuse and to make more reliable the design of H-MPSoC

- Chapter 6 presents the evaluation and validation of our framework through the use of two case-studies and several benchmarks.

- Chapter 7 concludes this thesis by summarizing its contributions and providing perspectives on future work.

# State of the Art

In this chapter we present the current state of the research in ESL tools for MPSoC, as well as for more specific domain related to a couple of contributions of our framework: the integration of HLS and the usage of Model-Driven Engineering approach in MPSoC design.

# 2.1 Ideal ESL Framework

In this section, we describe what we think would be the ideal framework flow, without caring about the feasibility aspect of it.

### Adaptability

This ideal framework should be adapted to several levels of expertise of designers: from software designers who have only little knowledge in hardware design to expert system designers. The former want to deal as little as possible with the hardware aspects and thus the framework should hide this level, should take all the design decisions and provides at the end a ready-to-implement system that satisfies the designer's constraints. Expert designers on the other hand, would use such framework in order to be relieved from tedious tasks that can be automated such as design cost and performance evaluation, software adaptation, communication interfaces generation, etc. This means that advanced-level designers should be able to express their expertise by being able to enforce design decisions they know will yield the best results.

### Inputs

So this ideal framework must allow designers to express their wishes with minimal efforts. On the application side, that would mean to be able to use the application code as input without any modifications and no limitation on the expressibility of the coding language accepted by the tool which, ideally, should be a widespread language (C, C++, etc.) or model formalism (UML, etc.). However that constraint is not realistic since most frameworks constrain only accept applications expressed in one or more Models of Computation (MoC). The architecture specifications/constraints should also be easy to express: this can be done through the use of component library and usage of a Graphical User Interface (GUI) that would help the designer visualize the design possibilities given

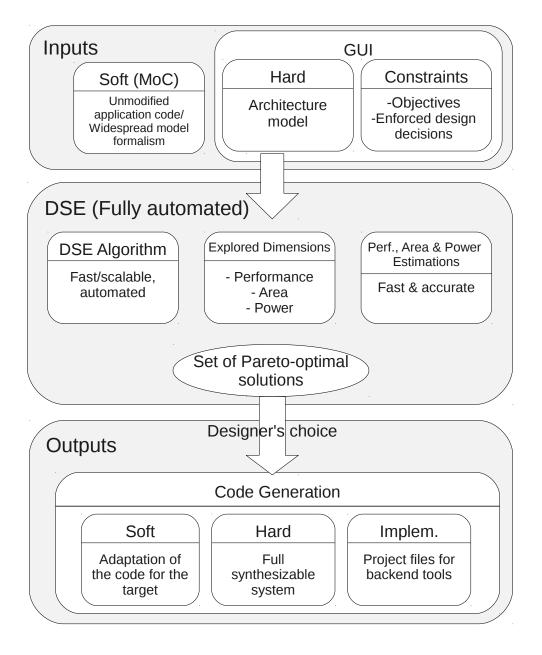

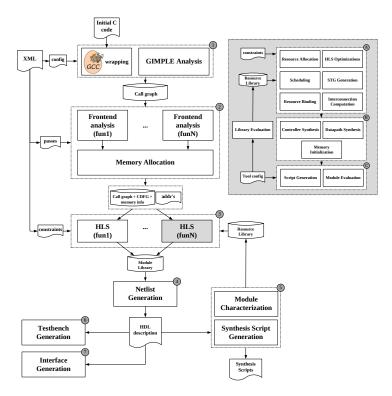

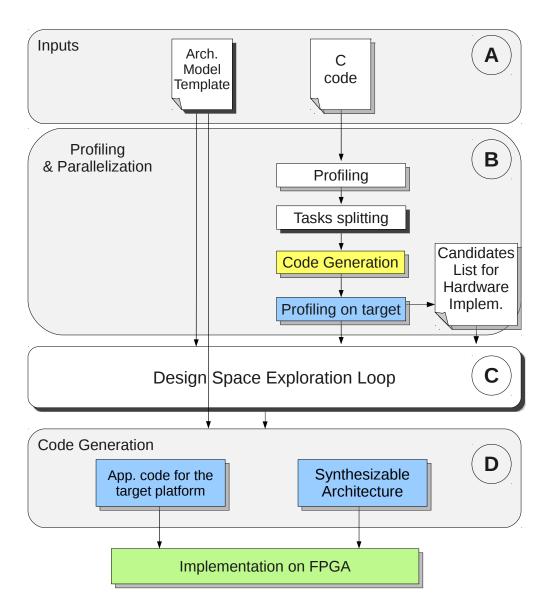

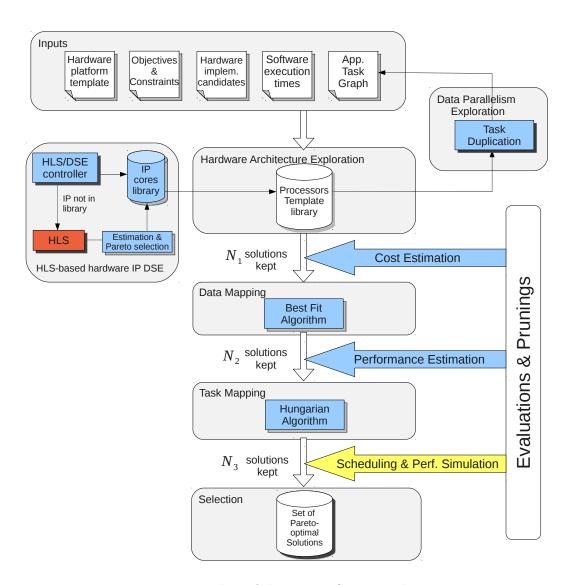

Figure 2.1: Ideal design flow for an H-MPSoC.

the current specifications and constraints. The tool should also give the possibility to advanced designers to express their expertise by letting them enforce specific design decisions. The characterization of the inputs should also be left as little as possible to the designers: for instance the software execution time of a task on a specific target should be measured through an automated on-target profiling or through an Instruction Set Simulator (ISS), the logic resource cost of hardware components should be provided whether from manufacturers documentation or through automated methods based on behavioral or logic synthesis, and so on.

# **Design Space Exploration**

Once the inputs are specified, the rest of the process should be fast, entirely automated and should return a ready-to-implement complete system that meets the designer's goal. Thus the DSE process:

- should be able to explore as many dimensions as possible: performance, area, power, etc. in order to offer designers a maximum of options;

- should be fast to explore a large number of designs or at least be scalable to let the designer choose between DSE speed and performance of the results;

- should integrate available debug and test tools;

- and should provide accurate estimations that faithfully reflect the characteristics of the final design.

### **Outputs**

The results of the DSE should be a set of Pareto optimal solutions giving a large number of quality solutions that offer tradeoffs between several criteria to the designer. The implementation files for the selected design should then be generated: the software code of the application is adapted, the hardware platform is synthesized and project files for implementation are generated, so that it can be directly implemented using the backend tool corresponding to the selected target (FPGA, ASIC, etc.).

# 2.2 Existing MPSoC Design Tools

Over the years, numerous tools and frameworks have been built for the design of architecture at the Electronic System-Level (ESL). This section presents a selection of such tools, and states the differences between them and our framework.

# 2.2.1 Daedalus

Daedalus [4] is a framework for the design of Heterogeneous MPSoC developed at the university of Amsterdam and Leiden. It is made of several tools, each performing a

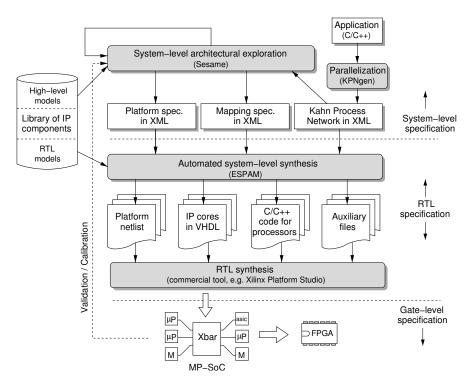

Figure 2.2: Design flow of Daedalus. Figure coming from [4].

different part of the design. KPNGen [5] generates a parallel version of the input application under the Kahn Process Network (KPN) formalism. Espam [6] deals with the code generation and the implementation files. Sesame [7] is a trace-based simulator which provides communication and performance estimations in order to evaluate the design under exploration. Daedalus starts by transforming the input sequential application into a Kahn Process Network version in order to exploit task-parallelism. For this it uses a tool named KPNGen that, provided that the input fulfill the requirements, automatically performs a series of transformations on the application: first it is transformed into a Single Assignment Code and from that version it produces the Polyhedral Reduced Dependency Graph (PRDG), and then the final KPN form of the application.

Then the KPN description is used as input for the Design Space Exploration. The explored dimensions are the number and the types of processing units, mappings and scheduling. The evaluation is based on traces of the application events during execution, which are read, write and execute events. These events are then used to simulate the execution of the application on the currently evaluated architecture. The results is a set of statistics which will help the designer chose the system best-fitting to his needs. Then the ESPAM tool checks some design rules constraints and generates the corresponding synthesizable code for implementation of the corresponding MPSoC solution.

Daedalus' design space exploration is based on an exhaustive exploration of the solutions based on the constraints given by the designer as input. Such an approach

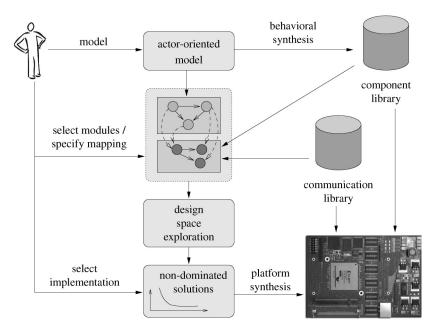

Figure 2.3: Design flow of SystemCoDesigner. Figure coming from [8].

can be terribly slow for loose exploration constraints leading to design spaces which cannot be entirely explored within a reasonable time.

# 2.2.2 SystemCoDesigner

SystemCoDesigner [8] is an automated framework for the exploration and the generation of the hardware and software of System-on-Chip for FPGA and developed at the university of Erlangen-Nuremberg. It uses as input an application described as an actor-oriented model communicating through FIFO in SysteMoC [9], a subset of the SystemC language. Then each actor undergo a behavioral synthesis with Forte Cynthesizer [10] in order to produce the corresponding hardware accelerator. In order to get accurate software execution times of the application, which are used for performance estimation, they have implemented a non-intrusive on-target profiling based on a hardware timer.

The design space exploration then begins, using a multiobjective evolutionary algorithm (MOEA). During DSE, partitioning and mapping decisions are taken for each actor and then performance of the designs, given as latency and throughput, are accurately estimated using Virtual Processing Components (VPC), an event-based simulator. The area cost is estimated based on the cost of the hardware components. Implementation of the communication are decided at this stage depending on the type of communication (software to hardware or hardware to hardware) and the available kinds of memory (e.g. BRAM, LUT, etc.). Since MOEA is a non-deterministic algorithm, several iterations can be performed in order to maximize the resulting set of non-dominated solutions. The final selected design is then generated for implementation

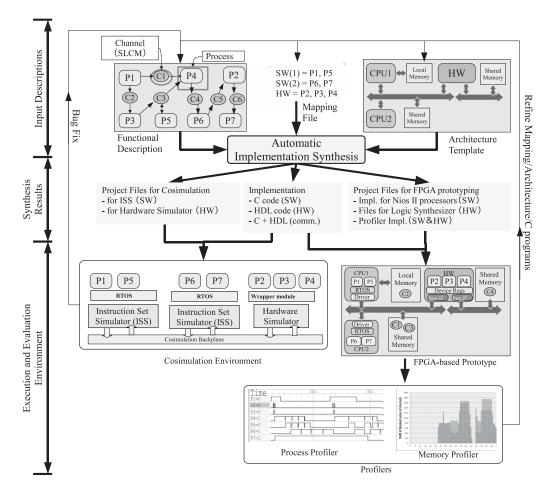

Figure 2.4: Design flow of Advanced Systembuilder. Figure coming from [11].

on the target FPGA: processors are instantiated as softcores, hardware accelerators are added to the design, communication interfaces are derived from the application model and are provided as a RTL description, the SysteMoC models of actors implemented in software are automatically converted to C++ and finally a bitstream for the target FPGA is generated.

In [8] are presented the results of an exploration with SystemCoDesigner for an MJPEG decoder. Although scalable, the DSE took over 2 days and 17 hours to evaluate 7600 solutions resulting in a set of 366 non-dominated solutions which is relatively slow compared to other solutions. They integrate HLS in their design flow however they do not take advantage of it to explore the possible tradeoffs between cost and performance by producing a series of accelerators with different characteristics, thus limiting their design space.

# 2.2.3 Advanced Systembuilder

Advanced Systembuilder [11] is a framework for automated synthesis of H-MPSoCs developed by the universities of Nagoya and Ritsumeikan. The inputs of the tool are:

- a functional description of the system using processes and channels with *System Level Communication Model* (SLCM);

- an architecture template which specifies the architecture with the available hardware components (number of processors, number of hardware accelerators, and the number of types of memories) and how they are assembled;

- a mapping specification.

These inputs must be manually specified by the designer. From these inputs, Advanced Systembuilder automatically perform several synthesizes: the hardware is generated through behavioral synthesis with the eXCite tool; the software is synthesized as a C code targeting a Real-Time Operating System (RTOS); communication are synthesized as Application Programming Interface (API) in the C code and as hardware components. In addition, two implementation outputs are produced: one is the files for cosimulation and the other one is the implementation files for typical FPGA backend tools such as Altera Quartus or xilinx ISE. These implementations are used to validate and evaluate the performance of the design.

To evaluate the performance of the prototype, Advanced Systembuilder seamlessly integrates into the FPGA design non-intrusive hardware memory and process profilers. The former measures the accesses to the memory along with the potential contention that can occur on the bus accessing the memory, and the latter profile the execution and idle time of the processes. With these measurements designers can decide if they are satisfied with the current design or can identify the points that needs improvement in his design (bottlenecks) and thus modify the design accordingly and relaunch a new iteration of Advanced Systembuilder with it.

The biggest lack in Advanced Systembuilder is that it does not perform any automated Design Space Exploration since mapping specifications and the hardware description of the system are provided by the designer as inputs. Moreover to evaluate the performance of a design, they whether rely on a slow Cycle-Accurate Byte-Accurate (CABA)simulation with ModelSim or onto an implementation on FPGA which implies a long implementation time. Consequently, exploring several designs is relatively slow: in [11], the evaluation of 24 designs required about five hours, most of it being due to the logic synthesis steps.

# 2.2.4 hArtes

hArtes [12] (Holistic Approach to Reconfigurable Real-Time Embedded Systems) is an European project which aims at developing a framework for hardware/software codesign. Three input formalisms are accepted for the application specification: C code, Scilab description (a software for numerical computation equivalent to MATLAB) or

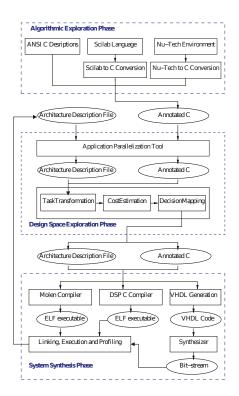

Figure 2.5: Design flow of hArtes. Figure coming from [12].

Nu-Tech description, a tool to design application in a graphical way. If the input is one of the latter two solutions, the equivalent C code is generated from the specifications in order to be used as input for the DSE. This C code is annotated with three different kinds of pragmas: pragmas that specify the possible parallelism of a section of code, pragmas that specify the profiling information of the program functions and pragmas that indicate tasks that can be accelerated through hardware. Those pragmas can be inserted whether manually by the designer or automatically by the tool during DSE. The hardware architecture specification is given as an XML file.

hArtes targets MOLEN architecture [13], which consists in the association of GPPs and specialized processing units (Intellectual Property (IP), Digital Signal Processor (DSP), etc.) on a reconfigurable unit. The application first starts by being parallelized with a dedicated tool. Then the DSE performs the mapping of the tasks, and the designs are then evaluated using the SoCLib modeling and simulation tool [14]. Then begin the so-called System Synthesis phase during which the annotated C code is compiled according to the mapping decision: whether with the MOLEN Compiler or with a DSP compiler. If a task is implemented in hardware, then the Dwarv tool [15] is called and generates an HDL version of the accelerator from the C code. So the final system implementation is the executable of the application and the bitstream of the hardware architecture.

The fact that hArtes allows several formalisms for the application specification allows to target a larger audience who may not be familiar with classical program-

Figure 2.6: Design flow of the Peace framework. Figure coming from [16].

ming language or model but who are used to numerical computation tools, such as mathematicians. However the fact that is necessary to provide an XML architecture description in input as well, which requires a bit of design knowledge to fill, kind of neutralize this advantage. In addition hArtes targets a specific type of architecture: the MOLEN paradigm, which is thus limiting the design possibilities.

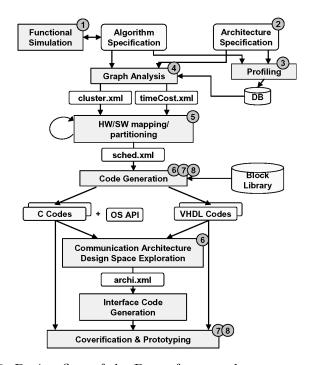

### 2.2.5 PeaCE

PeaCE [16] is a codesign tool for the design of systems for multimedia applications, developed by the CAP laboratory at Seoul National University. It is based on the Ptolemy framework [17], which is used for the design of real-time framework through modeling through extensive use of several models of computation and simulation. It starts from a model of an application using three different Model of Computation (MoC)s: one based on Synchronous DataFlow, called Synchronous Piggybacked Data Flow (SPDF) for the specification of computing tasks, another based on Finite State Machine (FSM), called flexible FSM (fFSM) for the specification of control task and another one, called task level-model that specifies high-level interactions between tasks. It also requires a set of the available architecture components (processors and IPs) to be used during the exploration step. The functional specification is used to generate a C code for functional simulation. Then for each task, performance measurements are made for each different processing unit with an ISS.

Then the first step of the DSE is launched: it explores the hardware solution, the partitioning and the mapping. Then code is generated for a hardware/software

cosimulation in order to get memory traces of the execution. These memory traces are then used during the second phase of the DSE where communication solutions are explored. In [16], only buses are considered as solution, so the DSE decides the number of buses, which bus is linked to which processing element and memory, bus frequency, etc. Finally, when a solution that satisfies the constraints has been found, implementation codes are generated for simulation tools and FPGA prototyping.

The advantages that PeaCE uses a model-driven approach to specify the input application by using and extending MoCs from the Ptolemy project, is also a limitation since designers have to learn how to model their applications with these three different MoCs instead of simply providing a C code, which is a widespread and well-known language among software designers. Moreover no exploration of the hardware acceleration is performed.

### 2.2.6 Xilinx XPS

Xilinx Platform Studio (XPS) [18] is a commercial design tool for systems targeting Xilinx FPGA devices. The design of the system can be made through the use of Graphical User Interface in order to add, remove and configure the elements of the hardware platform. It also provides several wizards to assist the designer in the creation of its system. It provides a library of proprietary IPs for the available bus and communication protocols, exploiting the board external peripherals. It also helps to integrate custom IP, through wizards and generation of interfaces in Hardware Description Language for integrating IP. The designed hardware can then be automatically transformed into a bitstream for the target FPGA through syntheses, mapping and placing and routing.

Although Xilinx recommends to use Xilinx Software Development Kit (SDK), a customization of the Eclipse framework, for managing the software aspect of the system, it is also possible to fully handle software project from XPS. This includes the compilation of the code as well as the specification of the drivers and the memory mapping.

While this tool, along with other Xilinx design tools, simplifies FPGA designs, it still remains a tool difficult to master and its numerous configuration options can often lead to bugs that can be hard to found/traced back at a later stage. The long synthesis times involved or the provided CABA simulation tool, *ModelSim*, do not allow to test quickly several designs and thus do not provide an adapted environment for design space exploration. So as such it should be used as a backend tool for implementation only.

# 2.2.7 Space CoDesign

Space Codesign [19] is a a commercial tool developed by SpaceStudio. Starting from an application specified in C code and split into tasks in order to express its parallelism and ease the mapping. Then the architecture must be described through a Graphical User Interface, this includes the number and types of processor, memories, buses along with the partitioning and mapping. Once the architecture specified, the architecture is estimated with the following criteria: performances, logic resources cost and power con-

sumption. This is done by generating SystemC TLM virtual platform of the hardware components and the C/C++ code of the software elements (tasks, RTOS). The generated virtual platforms includes non-intrusive profiling component for performances. The final design is selected based on the quality of results constraints provided by the designer and the corresponding hardware platform can be generated by another tool of SpaceStudio called GenX.

The limitation of Space Codesign is that, in spite of its GUI that allows to quickly modify the architecture and the partitioning, it does not perform any automated exploration.

# 2.2.8 Conclusion

Table 2.1 summarizes the presented ESL design frameworks. In the studied flow for H-MPSoC design, we can see that all of these tools failed to answer at least of the one of the problems stated in the introduction. For instance, Advanced Systembuilder, Space Codesign and Xilinx XPS do not perform any automated DSE, leaving to the designer the task to specify the evaluated architecture, which might be quite complex for a H-MPSoC. SystemCoDesigner and Daedalus are both too slow to be really efficient in an industrial context: the former because of its slow CABA-based performance estimation and the latter because of its exhaustive DSE. PeaCE has too complex input specifications and hArtes targets a specific kind of architecture, the MOLEN paradigm. Consequently there is a need for a new tool that will answers to these problems, by providing designers with a way to express their specifications with the level of details they wish, while automating the tedious aspects of design in order to provide quickly a satisfying implementation.

State of the Art

Table 2.1: Comparison of existing ESL frameworks.

|         |                          | ATT          |                           |    |      |                       |             |              |           |                       |             |         |         |             |                       |                    |               |            |         |           |       |            |                       |           |            |           |       |                            |            |        |                        |

|---------|--------------------------|--------------|---------------------------|----|------|-----------------------|-------------|--------------|-----------|-----------------------|-------------|---------|---------|-------------|-----------------------|--------------------|---------------|------------|---------|-----------|-------|------------|-----------------------|-----------|------------|-----------|-------|----------------------------|------------|--------|------------------------|

|         | Soft                     |              |                           |    |      | le Adapted            | code        |              |           |                       |             |         |         |             | le Adapted            | $_{\mathrm{code}}$ |               |            |         |           |       |            | le Adapted            | C++       |            |           |       | Adapted                    | C++        |        |                        |

| Outputs | Hard                     |              |                           |    |      | Synthesizable Adapted | Architec-   | $_{ m ture}$ |           |                       |             |         |         |             | Synthesizable Adapted | Arch.+             | imple-        | mentation  | files   |           |       |            | Synthesizable Adapted | Arch.+    | imple-     | mentation | files | $\operatorname{Bitstream}$ |            |        |                        |

|         | Code<br>gen-             | era-<br>tion |                           |    |      | Yes                   |             |              |           |                       |             |         |         | ,           | : Yes                 |                    |               |            |         |           |       |            | Yes                   |           |            |           |       | Yes                        |            |        |                        |

|         | Estima-<br>tions         |              |                           |    |      | Fast and              | accurate    |              |           |                       |             |         |         | ę           | Performance: Yes      | Trace-             | based         | simulation | / Cost: | Model-    | based | estimation | Trace-                | based     | simulation |           |       | Perf. with                 | VPC        |        |                        |

| DSE     | Explored di-<br>mensions |              |                           |    |      | Performance,          | area, power |              |           |                       |             |         |         |             | Architecture,         | Data & task        | mapping,      | Scheduling |         |           |       |            | Architecture,         | Mapping,  | Scheduling |           |       | Partitioning,              | mapping    |        | age                    |

|         | Scal-<br>able            |              |                           |    |      | Yes                   |             |              |           |                       |             |         |         | ,           | Yes                   | (brun-             | ing           | and        | con-    | straints) | `     |            | Yes                   |           |            |           |       | Yes                        |            |        | Continued on next page |

|         | Automated                |              | HM                        | IP |      | Yes                   |             |              |           |                       |             |         |         | ;           | Yes                   |                    |               |            |         |           |       |            | $N_{\rm o}$           |           |            |           |       | Yes No                     | <b>A</b> ) |        | ontinued               |

|         | Auto                     |              | $\mathbf{s}_{\mathbf{w}}$ | 3  | Arch | Yes                   |             |              |           |                       |             |         |         | ,           | Yes                   |                    |               |            |         |           |       |            | Yes                   |           |            |           |       | Yes                        | (MOE       |        | О                      |

|         | Constraints              |              |                           |    |      |                       | igne        | through a    | 105       |                       |             |         |         |             | •                     | $_{ m template}$   |               |            |         |           |       |            | XML files /           | GUI       |            |           |       |                            |            |        |                        |

| Inputs  | Hard                     |              |                           |    |      | Architecture          | template    | specified    | with mgn- | level Ior-<br>malisms | IIIdiibiiis |         |         |             | Architecture          | template           | in AADL       |            |         |           |       |            | Pearl De-             | scription | language   | + XML     | file  | N/A                        |            |        |                        |

|         | Soft                     |              |                           |    |      | Widespread            | well-       | known        | Input     | languages<br>/        | -101 .,     | malisms | with no | restriction | +                     | code in            | $_{ m SANLP}$ |            |         |           |       |            | C/C++                 | code in   | SANLP      |           |       | Actor-                     | oriented   | Model  |                        |

|         |                          |              |                           |    |      | Ideal                 | Frame       | work         |           |                       |             |         |         |             | Us                    |                    |               |            |         |           |       |            | Daedalus              |           |            |           |       | System-                    | CoDe-      | signer |                        |

|                                |                | Soft                         |                        |    |      | Ę                        | API for   | communi- | cation     |          |       |          |         |          |      |            |       | Compiled    | binary       |          |            | eC code +              | comm      |            |           |              |            |      |                        |

|--------------------------------|----------------|------------------------------|------------------------|----|------|--------------------------|-----------|----------|------------|----------|-------|----------|---------|----------|------|------------|-------|-------------|--------------|----------|------------|------------------------|-----------|------------|-----------|--------------|------------|------|------------------------|

|                                | Outputs        | Hard                         |                        |    |      | HLS                      |           |          |            |          |       |          |         |          |      |            |       | HLS with    | Dwarv        |          |            | Synthesizable C code + | Architec- | ture       |           |              |            |      |                        |

|                                |                | Code<br>gen-<br>era-<br>tion |                        |    |      | Yes                      |           |          |            |          |       |          |         |          |      |            |       | Yes         |              |          |            | n Yes.                 | simu-     | lation     | +         | imple-       | menta-     | tion |                        |

|                                |                | Estima-<br>tions             |                        |    |      | FPGA                     | proto-    | typing:  | inte-      | gration  | ot HW | profiler | /Gener- | ation of | CABA | simulation | files | SocLib      | perfor-      | mance    | estimation | Cosimulation Yes.      | / FPGA    | prototyp-  | ing       |              |            |      |                        |

| - Continued from previous page | DSE            | Explored di-<br>mensions     |                        |    |      | N/A                      |           |          |            |          |       |          |         |          |      |            |       | Application | parallelism, | mapping  |            | Two phases:            |           | tioning &  | mapping / | second: com- | munication |      | age                    |

| led from                       | _              | Scal-<br>able                |                        |    |      | N/A                      |           |          |            |          |       |          |         |          |      |            |       | $^{ m oN}$  |              |          |            | No                     |           |            |           |              |            |      | Continued on next page |

| Continu                        |                | Automated                    | $\mathbf{H}\mathbf{M}$ | IP |      | No                       |           |          |            |          |       |          |         |          |      |            |       | No          |              |          |            | No                     |           |            |           |              |            |      | ontinued               |

|                                |                | Auto                         | $\mathbf{S}\mathbf{W}$ | 3  | Arch | No                       |           |          |            |          |       |          |         |          |      |            |       | Yes         |              |          |            | Yes                    |           |            |           |              |            |      | O                      |

| Table 2.1                      |                | Constraints                  |                        |    |      | Mapping con-             | straints  |          |            |          |       |          |         |          |      |            |       | No          |              |          |            |                        |           |            |           |              |            |      |                        |

|                                | $_{ m Inputs}$ | Hard                         |                        |    |      | HW com-                  | ponents + | topology |            |          |       |          |         |          |      |            |       | XML file    |              |          |            | Set of                 | lable     | HW com-    | ponents   |              |            |      |                        |

| _                              |                | Soft                         |                        |    |      | Functional               | descrip-  | tion     | (process + | channel) |       |          |         |          |      |            |       | C code      | / Scilab     | language | / Nu-Tech  | SPDF /                 | fFSM /    | Task level | models of | computa-     | tion       |      |                        |

|                                |                |                              |                        |    |      | $\widetilde{A}dvanced$ - | System-   | builder  |            |          |       |          |         |          |      |            |       | hArtes      |              |          |            | PeaCE                  |           |            |           |              |            |      |                        |

State of the Art

| $\mathcal{O}_{U}$                        | uic     |                     | jι            | ne   | Л    | $T \iota$              |   |      |                |            |        |            |          |                |            |            |        |       |

|------------------------------------------|---------|---------------------|---------------|------|------|------------------------|---|------|----------------|------------|--------|------------|----------|----------------|------------|------------|--------|-------|

|                                          |         | Soft                |               |      |      |                        |   |      | Executable     | ELF        |        |            |          | C/C++          | adapted    | code       |        |       |

|                                          | Outputs | $\mathbf{Hard}$     |               |      |      |                        |   |      | Bitstream      |            |        |            |          | With ex-       | tra tool   | (SpaceS-   | tudio  | GenX) |

|                                          |         | Code                | gen-          | era- | tion |                        |   |      | ti <b>ð</b> ľo |            |        |            |          | Yes            | (with      | extra      | tools) |       |

|                                          |         | $\mathbf{Estima}$ - | $_{ m tions}$ |      |      |                        |   |      | ImplementatidΜ | cost /Pro- | filing | solutions  | provided | Cost, per-     | formance   | and power  |        |       |

| Table 2.1 – Continued from previous page | DSE     | Explored di-        | mensions      |      |      |                        |   |      | N/A            |            |        |            |          | N/A            |            |            |        |       |

| ed from                                  | П       | Scal-               | able          |      |      |                        |   |      | N/A            |            |        |            |          | N/A            |            |            |        |       |

| Continu                                  |         | Automated           |               |      |      | HM                     |   |      | No             |            |        |            |          | No             |            |            |        |       |

| e <b>2.1</b> –                           |         | Auto                |               |      |      | $\mathbf{S}\mathbf{W}$ | 3 | Arch | $^{ m oN}$     |            |        |            |          | No             |            |            |        |       |

| Tabl                                     |         | Constraints         |               |      |      |                        |   |      |                |            |        |            |          | Quality of Re- | sults      |            |        |       |

|                                          | Inputs  | Hard                |               |      |      |                        |   |      | AHDL           | compo-     | nent + | library of | IP       | XML file       |            |            |        |       |

|                                          |         | $\mathbf{Soft}$     |               |      |      |                        |   |      | C/C++          | code       |        |            |          | C/C++          | code split | into tasks |        |       |

|                                          |         |                     |               |      |      |                        |   |      | xuiliX         | XPS        |        |            |          | Space          | Codesign   |            |        |       |

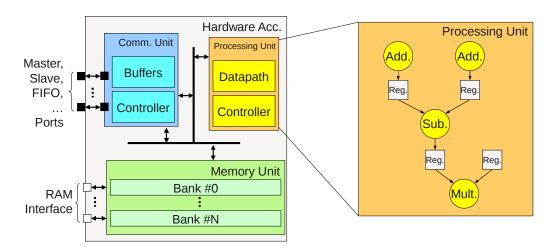

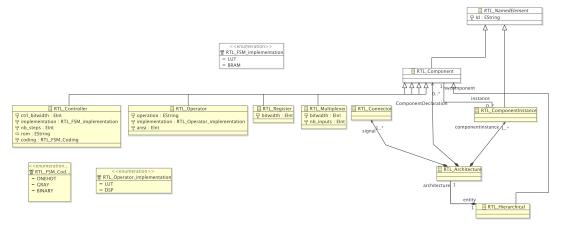

Figure 2.7: Architecture model of the hardware accelerator generated by GAUT.

# 2.3 High-Level Synthesis Tools

In H-MPSoC, hardware accelerators are used as a mean to speedup the system and it is part of the design space exploration to decide whether or not part of an application will be accelerated through hardware. If no off-the-shelf accelerator is available to the designer, it is possible to generate an IP through the use of HLS tool. It thus can be used as a tool in the ideal flow for H-MPSoC by providing synthesized on-the-fly hardware IP. In this section we present a few of the existing HLS tools.

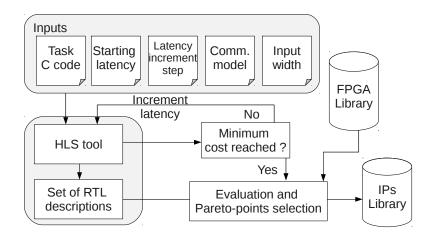

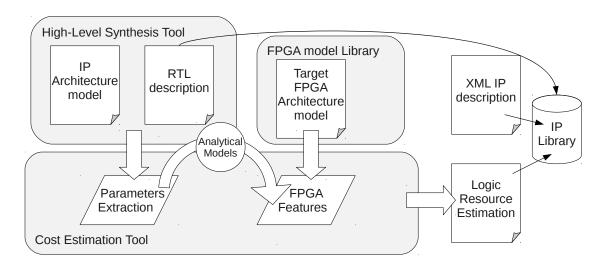

# 2.3.1 Gaut

GAUT [20] is a high-level synthesis tool that can generate hardware accelerators from a behavioral C/C++ specification. It has been being developed for 15 years at ENSSAT Lannion and the Université de Bretagne-Sud Lab-STICC laboratory. The synthesis is performed under a time constraint according to:

- a generic architecture model as illustrated by Figure 2.7;

- a library of pre-characterized Functional Units (FU), i.e. basic operators such as adders, multipliers and hierarchically designed IPs;

- and a communication interface choice: FIFO or Ping-Pong memory.

The generated hardware block comes in different formalisms including VHDL and System C. Communication interfaces can be tuned to include specific features such as the Xilinx Fast Simplex Link (FSL) [21]. It is used in our framework to generate series of hardware IP during the hardware accelerators design space exploration which is detailed in Section 4.3. This tool is based on fast scheduling and allocation heuristics, it produces a RTL code compliant with a register-to-register architecture model. It is

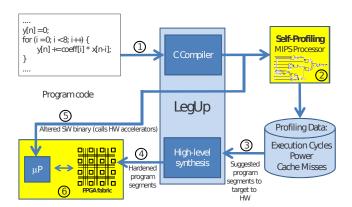

Figure 2.8: Design flow of the LegUp framework. Figure coming from [22].

decoupled from Logic Synthesis tools and has a linear computational complexity that we exploit to get fast accelerator evaluation within the whole H-MPSoC DSE loop.

# 2.3.2 LegUp

LegUp [22] is a research tool developed at the university of Toronto that semi automatically accelerates part of an application by generating and integrating a hardware accelerator into the design. It starts by performing an automated profiling of the application thanks to a modified MIPS processor-based FPGA implementation. The MIPS is modified in order to perform the profiling of its own execution. With this profiling, the parts of the applications to be accelerated through hardware are synthesized with LegUp behavioral synthesis tool. Then the software code of application is modified in order to call the generated hardware accelerators. Finally the software code is compiled and the hardware architecture is implemented on the FPGA, resulting in the implementation of a complete system.

LegUp is a quite complete tool for hardware acceleration of an application and is adapted to software designers that are not familiar with hardware design. However, LegUp does not actually performs any design space exploration: mapping and hardware decisions are taken manually by the designer, and the rest of the hardware architecture is determined prior to hardware synthesis.

# 2.3.3 C2H

The NIOS C2H compiler [23] is a tool that generates IP cores from a C specification. This tool provides an easy way to generate accelerators but does not perform any real high-level synthesis. Contrary to what is done by C2H, HLS means resources allocation and scheduling according to a predefined architecture model that also makes fast estimation possible. The synthesis from C2H or equivalent C-to-VHDL compilers could however be considered as additional solutions to feed the IP database used during DSE.

Figure 2.9: Design flow of Bambu. Figure coming from [25].

# 2.3.4 CyberWorkBench (CWB)

CyberWorkBench [24] is an impressive and complete but also commercial framework proposed by NEC, it relies on different HLS tools (data-dominated, control-dominated, control-flow intensive, ASIP design). This framework provides simulation and area/performance/power estimation tools for various FPGA technologies. The DSE tool is based on the modification of code (C/SystemC) annotation, such as for instance loop unrolling. However, we also observe that DSE includes low level logic synthesis tools that mean long synthesis time. Moreover the hardware/software mapping remains manual as well as the function/task/instruction parallelisms and the choice of I/O parallelism and protocols. This is a set of tools that do not exactly pursue the same objective as we aim to do, namely a fast exploration based at the task level on hardware/software partitioning and processor specialization and at the hardware accelerator level on the automatic exploration of instruction and I/O parallelism.

# 2.3.5 Bambu

Bambu [25] is a framework developed at Polimi which aims at the automated HLS of application. It takes as inputs the C code of an application and an XML file that specifies constraints and options of the flow. The input is transformed in a Static Single Assignment form through a modified version of the GCC front-end and undergoes a

series of simple optimizations, such as dead code removal, loop unrolling, constant propagation, etc. Then data are allocated on the available memories based on the application graph analysis and the constraints provided by the designer as inputs. Then, for each function of the C code, an HLS creates the functional hardware equivalent including datapath, controllers and memory interfaces. Several options are given to the designer for the HLS, offering tradeoff between area and performances. It supports generation of the implementation files of the final system, for several backend tools for FPGA (Xilinx, Altera...) as well as for ASIC. It can also generate testbenches for simulation tools and check that the synthesized system is functionally equivalent to the software application given as input.

Bambu is limited in the solutions it can provide as it can only generate full hardware system. This means that it does not deal with the software aspect of the system, thus leaving out of the exploration of data-parallelism and restricting the design possibilities offered to the designer and thus is not appropriate for the design of H-MPSoC.

# 2.3.6 AutoESL's AutoPilot

AutoPilot [26] is a high-level synthesis developed by AutoESL and now belonging to Xilinx<sup>1</sup>. Starting from high-level specifications it can provide the outputs RTL in VHDL, Verilog and SystemVerilog. It also provides a cost estimation of the FPGA logic resource as well performance — latency and throughput — at function and loop granularity which allow designers to optimize their code precisely.

One of the lack of AutoPilot is the impossibility to specify timing constraints on the input/output.

### 2.3.7 Conclusion

From this study of HLS tools, we can give a list that could be integrated into our framework to be used for hardware accelerators exploration (described in Section 4.3). The tools that can be used are: Legup, Bambu, AutoESL and Gaut. C2H cannot be used since strictly speaking, it does not perform HLS.

# 2.4 MDE-based Design of MPSoC

Several attempts have already been made to introduce Model-Driven Engineering into methodologies for MPSoC designs. We detail our usage of MDE in Chapter 5.

# 2.4.1 Model Driven Engineering for MPSoC DSE

In [27], a DSE methodology based on Model-Driven Engineering is proposed for MPSoC. Models are UML-based models and are implemented with the ModES framework which provides the necessary meta-models, as well as a transformation engine in order to

<sup>&</sup>lt;sup>1</sup>which renamed it Vivado HLS.

translate model from one formalism to another. The models are divided into four domains:

- an application domain, which describes the tasks of the application

- a platform domain, which described the hardware components of the architecture

- a mapping domain, which describes the mapping between the task and the processors

- an implementation domain, which describes the info for synthesizing/implement the system

A library of components is provided to describe the hardware architecture. DSE is implemented as a heuristic based on simulated annealing which aims to minimize the following system characteristics: communication, memory, performance and power consumption. In order to perform evaluation of a design during DSE, it is necessary that the designer provide measurement of the performance, cost and power. For the software, this is done by compiling the code on the target architecture. DSE is performed by the H-Spex tools which explores the following characteristics for each processor: their numbers, the mapping of tasks onto them, the assignment of buses and its voltage. The components are stored in a repository with the characteristics necessary for evaluation of the system during DSE such as their size, their power consumption, their performance, etc. Once the DSE is over, a model of the final system is produced and through model transformation the final implementation files are generated. Their DSE is quite fast and accurate since in [27], it manages to evaluate a thousand designs in about one hour with very few error on the estimated values.

In this framework, MDE is used for model transformation, including the final implementation files, design-rules verification, and design space exploration. However they relies on the designer to provide all the necessary measurements values such as performance, cost, consumption for every hardware components and application task models. These values are quite important since the accuracy of the final implementation characteristics depends on the accuracy of the provided measurements. While they provide a technique for the software components, they are very evasive on how they get these measurements for hardware components, relying on the assumption that the component will be already present in the component repository.

# 2.4.2 Multilevel MPSoC Simulation using an MDE Approach

In [28] is presented an MDE-based DSE for MPSoC. The tool starts from description of a system, including thee application and the architecture, in the MARTE [29] formalism, which is an extension of UML for embedded and real-time systems. Then the DSE process is performed through successive simulations at different granularities. The simulation implementations are based on the SystemC language. At first a fast coarse granularity simulation (TLM PVT) is performed, checking for functional verification and contention detection, and allowing to quickly estimate a lot of solutions. Then,

from these estimations a selection is made which is then evaluated more accurately with a slower finer grained simulator (CABA). MDE is here used for automated model-to-model transformations, more specifically from the MARTE description to the different levels of simulation in SystemC.

While this presented methodology seems quite efficient for Design Space Exploration, it could be further enhanced by adding the possibility to generate the final implementation code of the system not just a simulation implementation. This would allow to have a more complete framework. Also, the authors provides no method to get the values (performance, cost, etc.) to characterize the models for evaluating a system during DSE, leaving this task to the designer. Furthermore, they consider only performance and power during DSE, and not logic resources cost, which can be problematic in an embedded system environment.

# 2.4.3 A Co-design Approach for Embedded System Modeling and Code Generation with UML and MARTE

In [30] and [31], a methodology is presented for the design of MPSoC. The models of both the application and the platform must be provided as MARTE and UML models. From this description, it possible to generate the synthesizable hardware components, whether through synthesis or through reuse of existing components. The project implementation files for Xilinx backend tools are also generated so that the project can directly be implemented on the FPGA target. Moreover it provides a way to model the dynamic comportment of a component thus allowing the take into account the dynamic reconfigurability of the FPGA. This allows the generation of system that uses dynamic reconfigurability and thus bring reconfiguration to novice designers.

The possibility to generate a complete from an abstract specification allows even designers unfamiliar with hardware design (typically, software engineers) to implement an hardware version of their systems. However the DSE is still a manual task that remains under the designer responsibility.

# 2.4.4 Conclusion

Among the studied MPSoC flows using MDE techniques for MPSoC design, one does not perform automated DSE, one does not generate the implementation files for the selected design and the last one does not provide any solution to get hardware characteristics values. So while there exists design tools that integrate MDE methods as part of their design flow, none of them are fully satisfying in regards to the problems stated in the introduction.

# 3

# Flow of the Framework

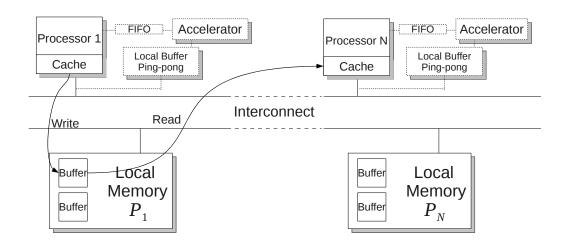

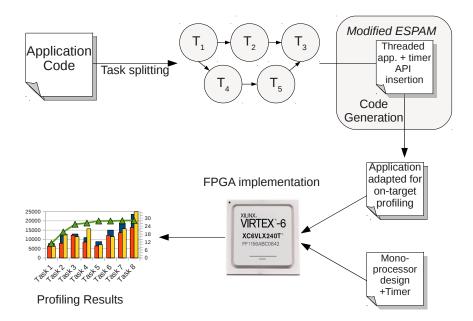

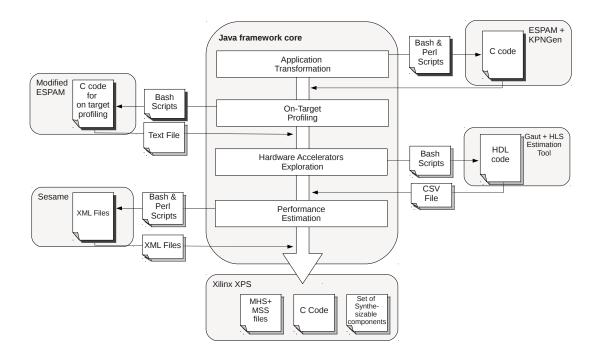

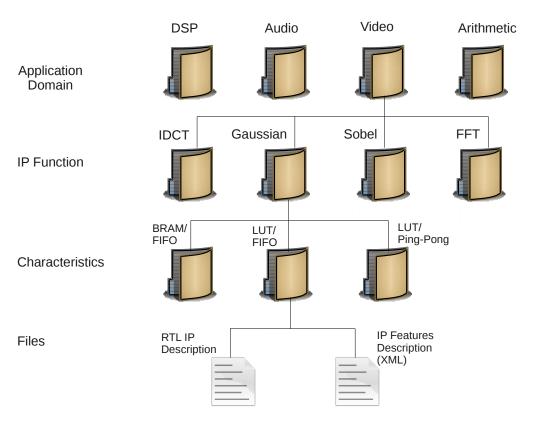

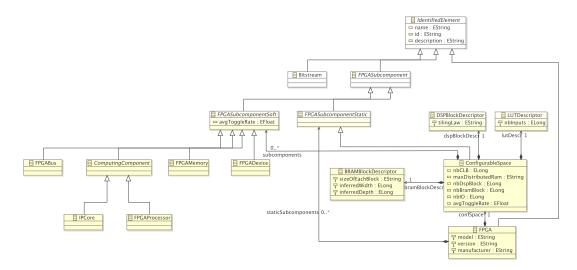

In this chapter, the framework flow is introduced. First it presents the tool implementation and gives a rapid overview of the steps composing the design flow, from inputs to outputs through design space exploration and details some parts of the flow that do not represent major contributions of this thesis. The used formalism as well as the target architecture are explained. External tools that were used to perform some steps of the flow are introduced. Finally, we present how we used databases in order to favor reuse.

# 3.1 Flow Global Overview

This section presents the detailed implementation of our tool, the target architecture of the flow, its inputs and a general description of how it works.

# 3.1.1 Tool Implementation

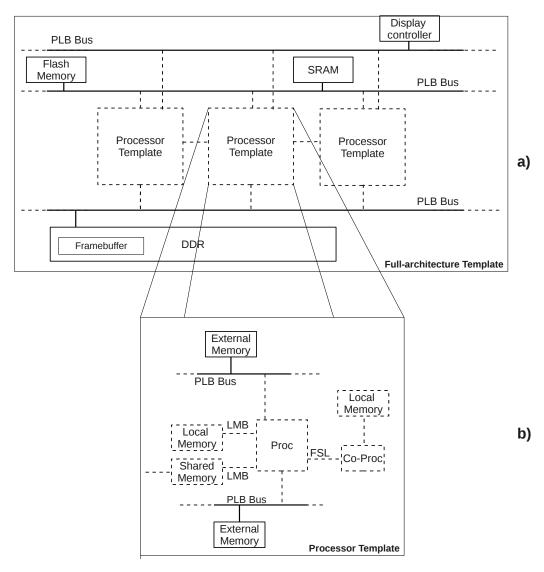

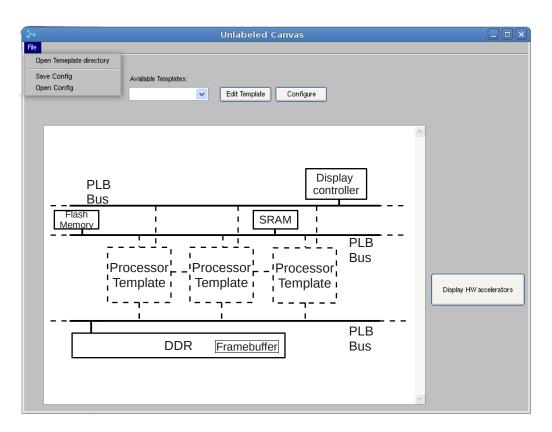

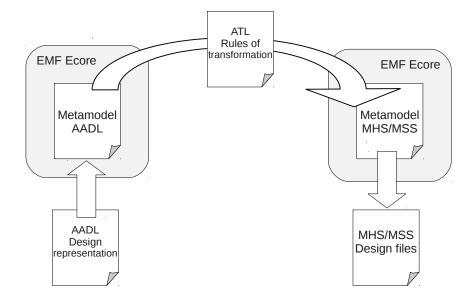

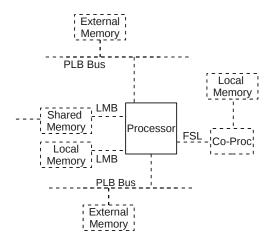

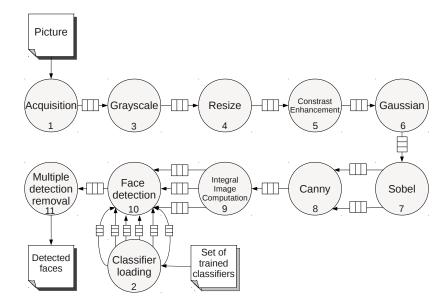

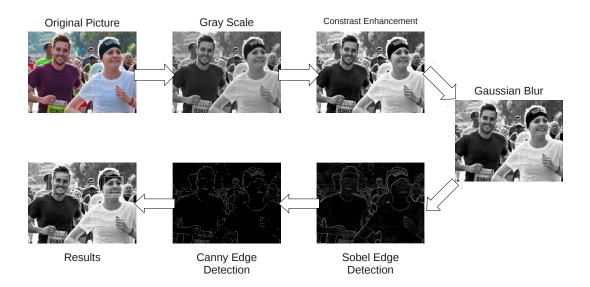

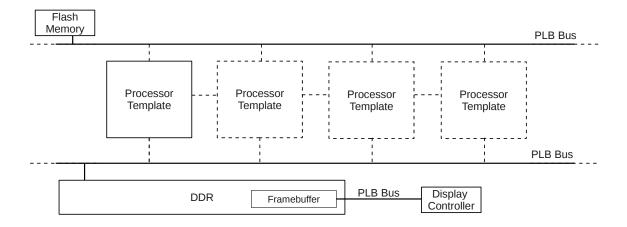

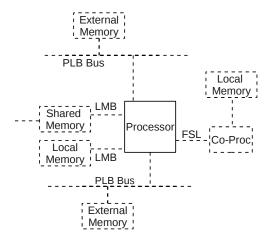

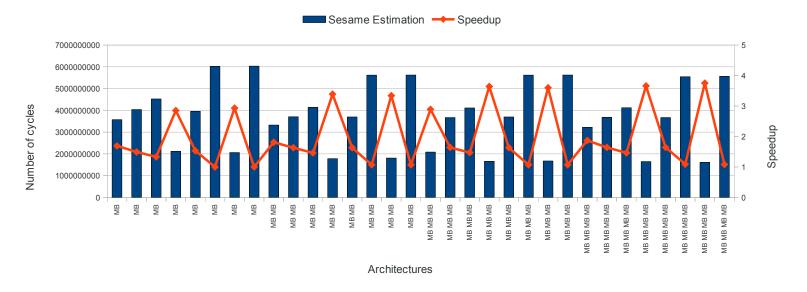

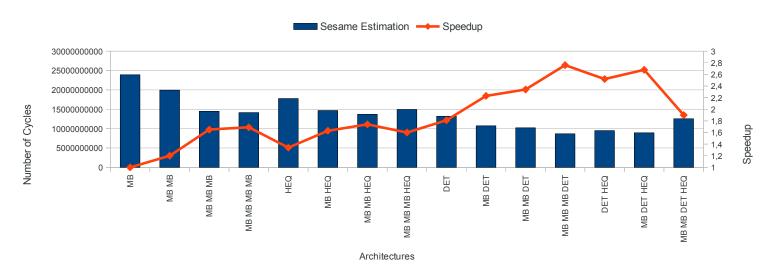

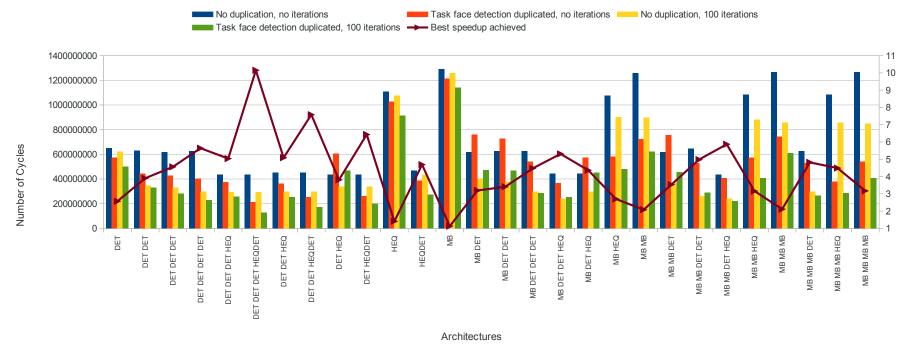

Our framework is a combination of several tools and technologies. Its core has been written in Java language in order to benefit from its portability, its widespread use among software developers and its object-oriented paradigm. It was developed with the open-source IDE, Eclipse [32], which has a large and active community as well as numerous plugins to assist programmers in the development of applications. It also possesses several Java class libraries such as EMF which provides functionalities for the integration of MDE techniques.