ARGEN

Overlays offer the promise of a full portability between vendors and parts

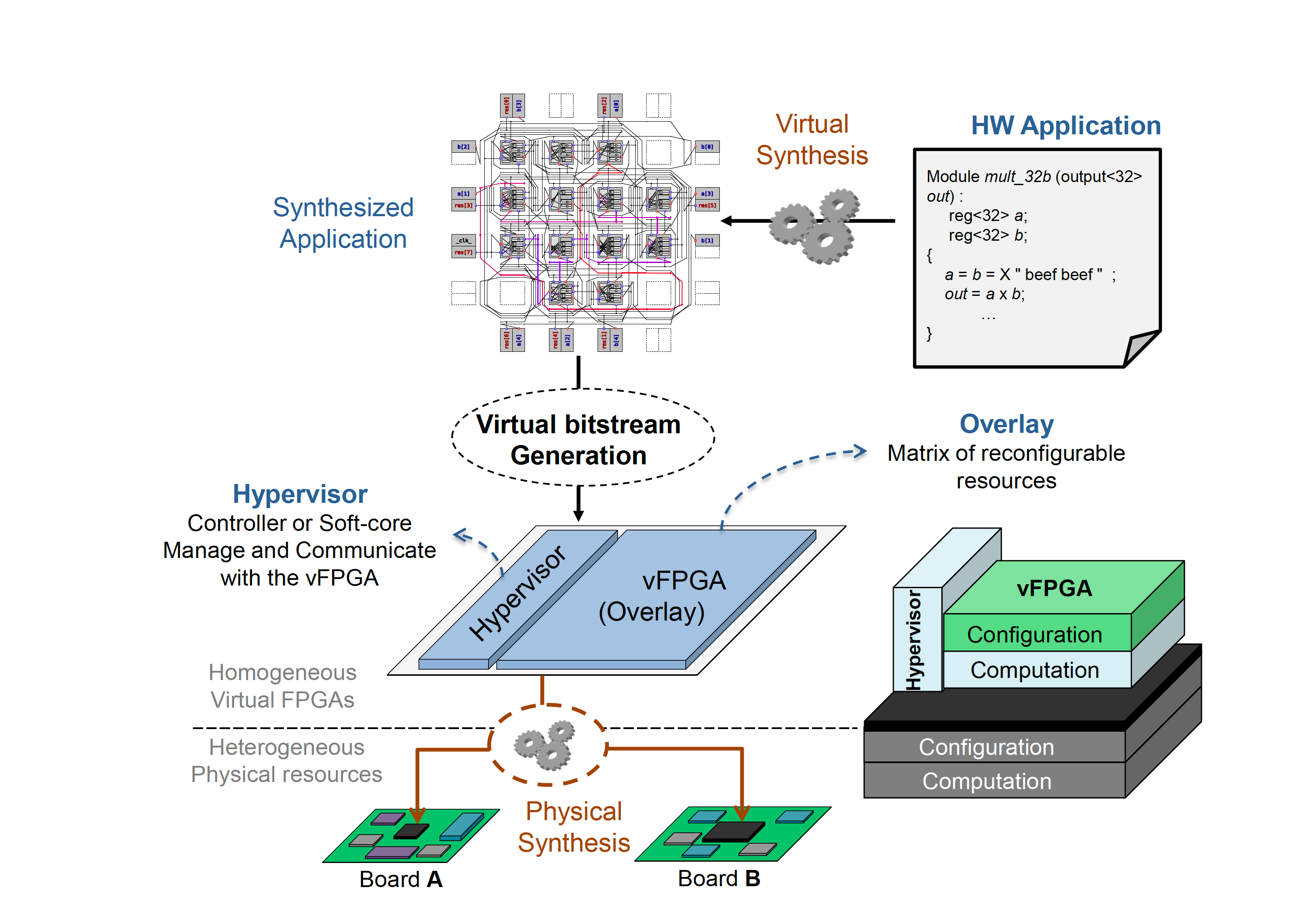

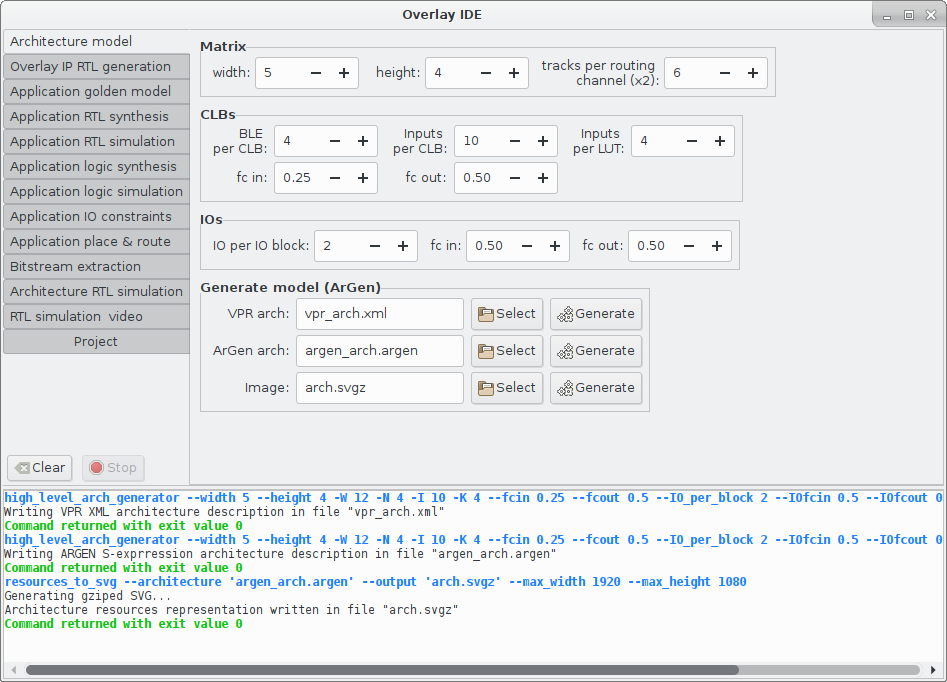

when implementing hardware designs.However the complexity to design, explore and make use of such overlays prevents from a massive adoption especially by software engineers. ARGEN is a downloadable integrated tool flow that supports defining reconfigurable architecture and generating the corresponding overlay along with its System-on-chip exploitation environment.

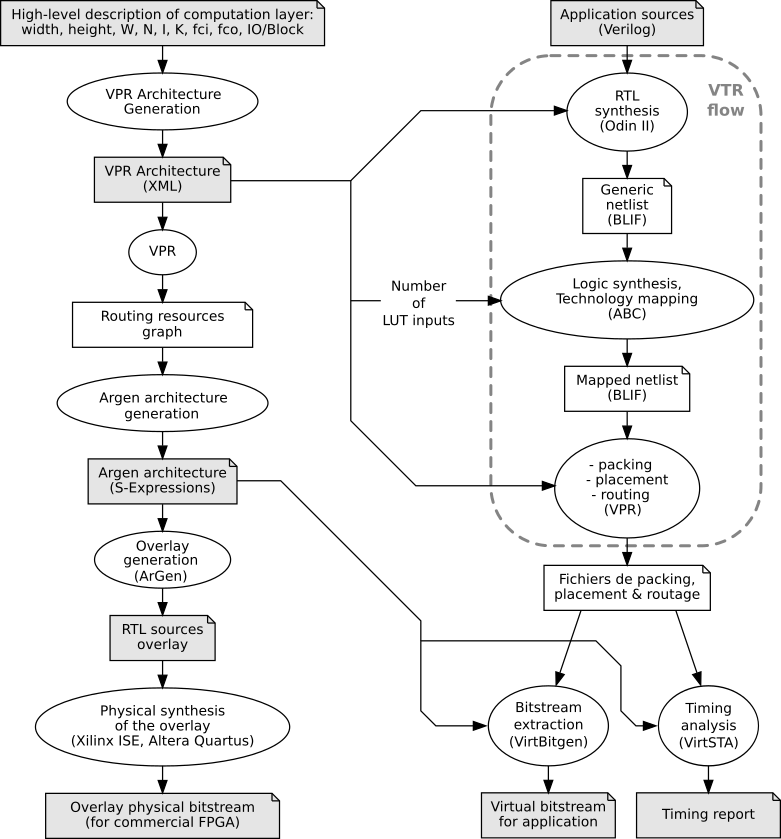

The ARGEN Flow is described below:

The tools process the output of the well known academic tool VPR.

Several parameters are injected in the flow so that to produce the VPR compliant architecture, hence gaining the ability to Place and Route circuits. The VPR's output is further processed to generate a valid bitstream. The bitstream can then configure the architecture that ARGEN has generated as VHDLcode.

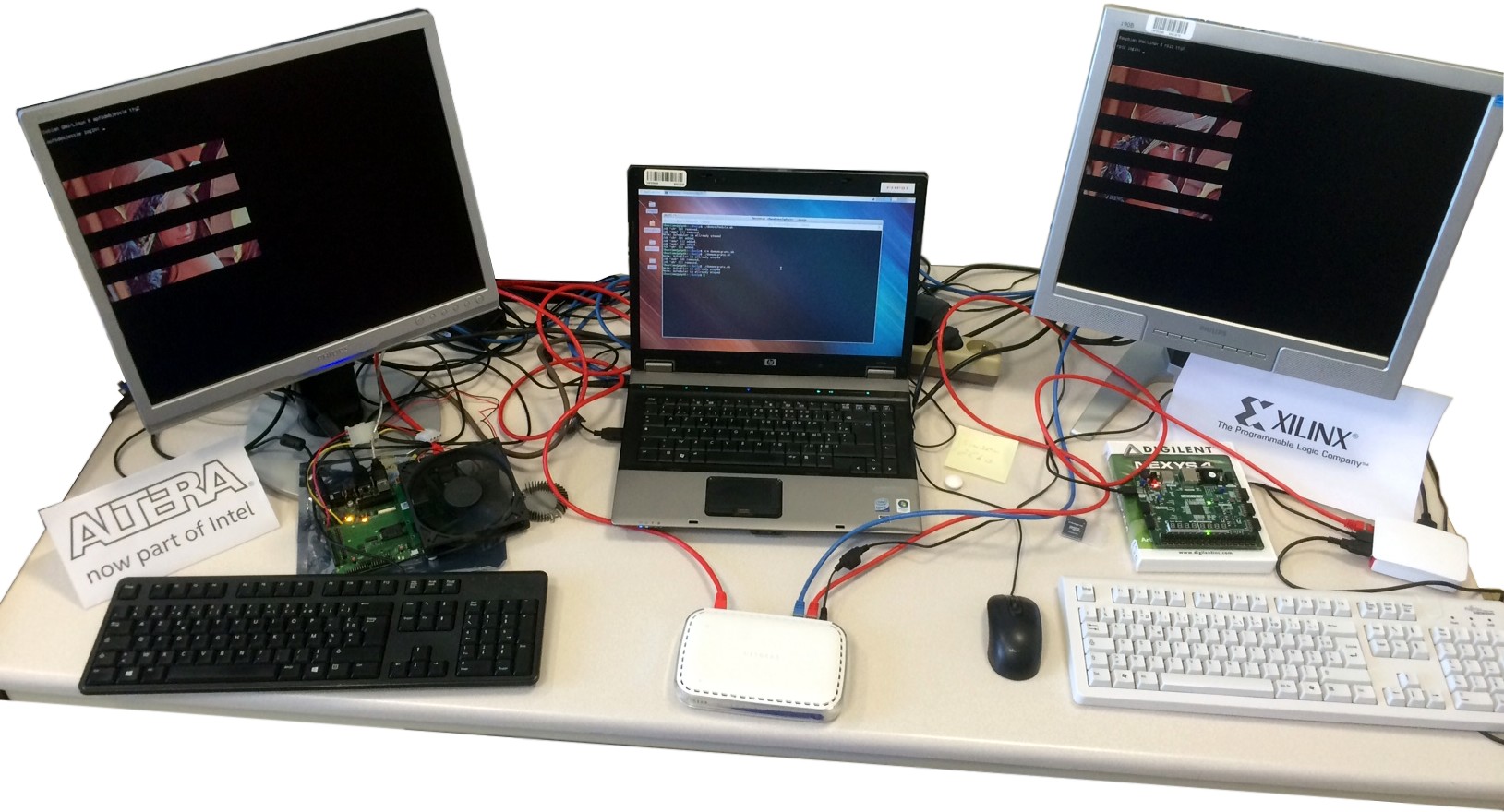

A simple integration platform has been design (ZeFF), with a softcore serving as a controller for the overlay. One benefit is portability over devices as illustrated below (ping pong computation with state snapshot/marshling/restore, same bitstream, two targets from Xilinx and Altera).

The end to end solution illustrated by the video below, where yellow lines are set to one. Note that segmented routing is visible when signals' value spreads over routing.